# IM283 Low-voltage RFID reader IC for 125kHz tags

# **DATA SHEET**

# **Typical Applications**

- ➔ Integrated RFID base-stations

- ➔ RFID reader-writers

- ➔ Car immobiliser

- → Low voltage portable readers

### **Features**

- → Low voltage down to 2.5 volts

- ➔ Read and Write capabilities.

- ➔ Includes a full ID processing for EM4100 and EM4200\* series

- ➔ Supported frequency range: 100 to 150 kHz

- → Optimization of reading conditions by using RTA<sup>™</sup>: unique readertransponder self-adapting technique.

- ➔ High-power dual antena drive.

- → 100% and 50% modulation write capability.

- → Multiple data rates: 2kbit/s, 4kbit/s, 8kbit/s.

- ➔ Operating temperture range: -40 to +85°C

Plastic SO18

# **Product Description**

The IM283 is a fully-integrated 125 kHz RFID reader circuit. It is specially designed for being a space and cost efficient kernel IC of an RFID reading and writing base station. It covers the digital real time functions and the analogue signal processing necessary to access standard 64-bits transponders available on the market. IM283 is accessible by a standard micro – controller as an intelligent front - end

(\*) using EM4100 / 4102 protocols

peripheral device. A unique mutual tuning capability (RTA<sup>TM</sup>) allows dynamic adaptation to every transponder read, particularly in poor reading conditions. IM283 is versatile enough to work in most low-power (short distance) and high power (longer distance) applications. IM283 is fully compatible with latest version of SW016 reader IC.

# **Table of contents**

| 1 | PRO                              | DUCT OVERVIEW                                                                                                                                                                                                                                                    | 3              |

|---|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 1.2<br>1.3<br>1.4<br>1.5         | GENERAL DESCRIPTION<br>BLOCK DIAGRAM<br>I/O DESCRIPTION<br>PACKAGE OUTLINE<br>TYPICAL APPLICATION SCHEMATICS<br>PACKING & ORDERING INFORMATION                                                                                                                   |                |

| 2 | DET                              | AILED DESCRIPTION                                                                                                                                                                                                                                                | 7              |

| - |                                  | P ID transfer protocol<br>B Decoding of the input stream                                                                                                                                                                                                         |                |

| 3 | ELE                              | CTRICAL CHARACTERISTICS                                                                                                                                                                                                                                          | 14             |

|   | 3.2<br>3.3<br>3.4                | ABSOLUTE MAXIMUM RATINGS<br>OPERATING CONDITIONS<br>TIMING CHARACTERISTICS<br>DC CHARACTERISTICS<br>I/O CELLS                                                                                                                                                    | 14<br>14<br>15 |

| 4 | APP                              | LICATION NOTES                                                                                                                                                                                                                                                   | 16             |

|   | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4 | <ul> <li>Application Schematics – for 50% Modulation if tag is in read/write mode</li> <li>Application schematics for read only tags</li> <li>Application schematics for 100% Modulation if tag is in read/write mode</li> <li>HIGH POWER APPLICATION</li> </ul> |                |

| 5 | ΝΟΤ                              | ES                                                                                                                                                                                                                                                               | 22             |

# **1 Product Overview**

### **1.1** General Description

IM283 is a fully integrated RFID reader / writer that can be used as the dedicated RFID peripheral of your RFID base-station.

Adapted to EM410x transponders, IM283 enables a whole-in-one processing of 64-bits standard tags. it processes reading of the raw tag ID string, then performs dynamic parity and Manchester integrity checks and finally bufferizes the 40bits of usable ID code for the micro to stream out serially.

IM283 provides full a compatibility with old SW016 reader IC.

- Auto oscillation between OSC\_OUT1 (and/or OSC\_OUT2) and OSC\_IN

- Possibility to drive OSC\_IN with a 125kHz (100 150kHz) to fix the carrier frequency

- External envelope detection

- Internal filtering (sensitivity: 1mV rms)

- Digital-block functions identical to existing SW016 decoding of Manchester coded input stream

- Writing capability

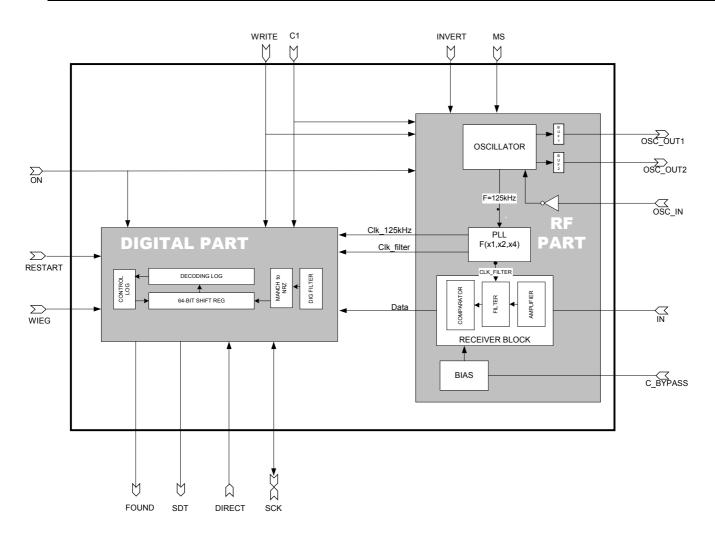

# 1.2 Block Diagram

# 1.3 I/O Description

#### Table.1 General pin description

| Package Pin<br># | Die-pad<br>Name | I/О Туре |

|------------------|-----------------|----------|

| 1                | INVERT          | In       |

| 2                | WRITE           | In       |

| 3                | RESTART         | In       |

| 4                | FOUND           | Out      |

| 5                | SCK             | In/Out   |

| 6                | SDT             | Out      |

| 7                | C1              | In       |

| 8                | MS              | In       |

| 9                | GND             |          |

| 10               | DIRECT          | In       |

| 11               | C_BYPASS        | In       |

| 12               | IN              | In       |

| 13               | OSC_IN          | In       |

| 14               | OSC_OUT2        | Out      |

| 15               | OSC_OUT1        | Out      |

| 16               | ON              | In       |

| 17               | VDDA            |          |

| 18               | VDD             |          |

SOIC 18

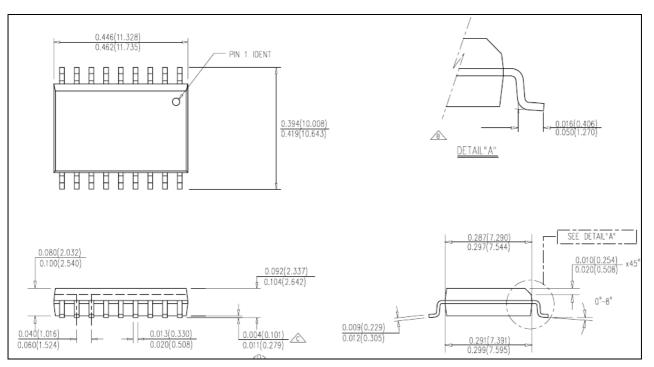

## 1.4 Package outline

#### SOIC 18 PACKAGE

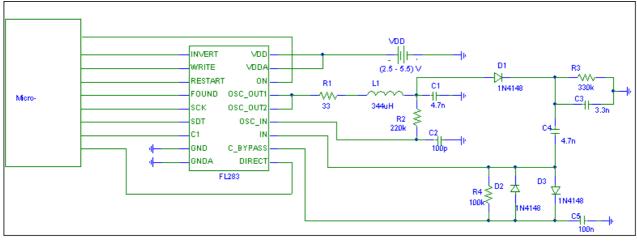

# 1.5 Typical application schematics

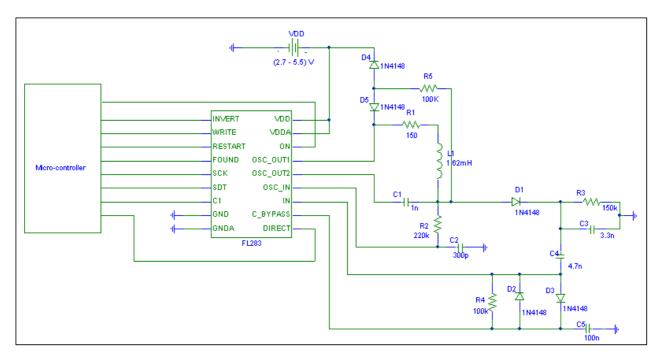

#### Fig. 1 : Application drawing (short distance reader)

# 1.6 Packing & Ordering information

- Standard packing: antistatic clear tubes

- Base quantity: 2000

<u>Note</u>: for smaller quantities, please check with your local distributor.

#### Table.2 Ordering codes

| Product description | Package | Ordering code | Notice |

|---------------------|---------|---------------|--------|

| IM283               | SOIC18  | IM283A-FT     | -      |

# 2 Detailed description

#### 2.1 Overview

Particularly dedicated to EM410x transponders, IM283 enables a whole-in-one processing of 64-bits standard tags. No stream decoding is necessary: IM283 reads the tags and stores the ID code for the host (micro-controller) to read whenever it can. IM283 then work as a pure slave peripheral and does not require any real-time resource from the host.

For customers who have been using the old SW016, IM283 will ensure full compatibility in their application.

- IM283 is set by leaving pin <u>DIRECT unconnected</u> (or connected to ground)

- IM283 is controlled by and external microcontroller, which provides the necessary control signals to:

- Switch on and off (stand-by mode) IM283

- Reset IM283 to restart ID searching (RESTARTcommand)

- Send a SCK signal to clock the serial data bit stream store into IM283

In return, it receives from IM283:

- The indication that an ID has been successfully read (FOUND signal)

- An error free ID number as a raw serial NRZ data

- The power output drives an antenna (coil) tuned to the right frequency and connected to the OSC\_OUT1 pin provides a 125 Khz carrier.

The amplitude-modulated signal due to the response of the tag is superimposed to the main carrier. A simple diode and an RC network provide a first level of filtering to leave out the high amplitude carrier from the small feedback signal.

Additional on-chip filtering provides further rejection of mains disturbance and remaining carrier before full synchronization, demodulation and error checking.

#### 2.2 Data Frame Check

A state machine is implemented for data integrity checking. The following states are sequenced:

#### **STATE 1**: Wait for header.

This state is valid after RESTART. Internal 64-bit shift register is reset and then data acquisition is performed.

#### **STATE 2**: Data format check.

This state is valid after STATE 1. In this state, the incoming data is checked for correct parity and for header + stop bit integrity.

If an error occurs, then the system goes back to STATE 1. If no error - then STATE 3.

**STATE 3**: Ready for data transfer.

This state follows STATE 2 when there was no error in received data frame.

FOUND signal is asserted active high and remains active while STATE 3 is valid.

Digital part is ready to output serial data to the microcontroller.

STATE 3 is a stable state: it does not change unless a proper RESTART command is provided.

With a RESTART command the system goes back to STATE 1.

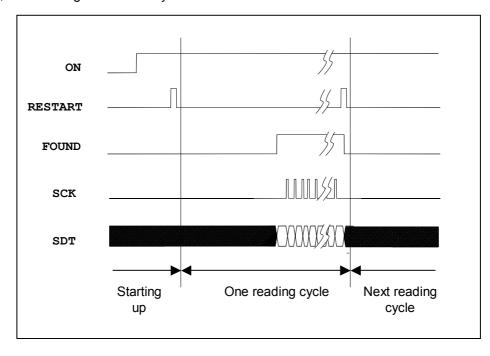

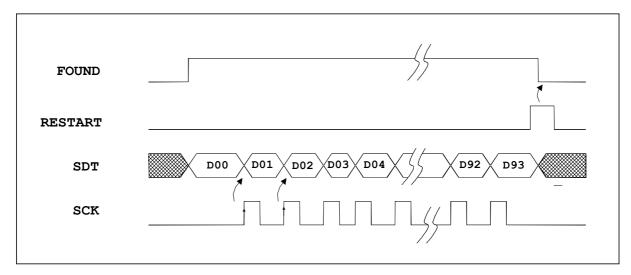

## 2.2.1 ID transfert protocol

IM283 is fully compatible with Marin EM4001, EM4002 EM4100 and EM4102 tags or 64-bits standard transponders of which the memory array is organized as:

| 1      | 1        | 1  | 1 | 1   | 1   | 1   | 1   | 1  | - 9bits header                                                  |

|--------|----------|----|---|-----|-----|-----|-----|----|-----------------------------------------------------------------|

| 8 vers | ion bits | or |   | D00 | D01 | D02 | D03 | P0 | - 4data bit &                                                   |

| custor | ner ID   |    |   | D10 | D11 | D12 | D13 | P1 | - associated                                                    |

|        |          |    |   | D20 | D21 | D22 | D23 | P2 | even row                                                        |

|        |          |    |   | D30 | D31 | D32 | D33 | P3 | parity bit                                                      |

|        |          |    |   | D40 | D41 | D42 | D43 | P4 |                                                                 |

|        |          |    |   | D50 | D51 | D52 | D53 | P5 |                                                                 |

|        |          |    |   | D60 | D61 | D62 | D63 | P6 |                                                                 |

|        |          |    |   | D70 | D71 | D72 | D73 | P7 |                                                                 |

|        |          |    |   | D80 | D81 | D82 | D83 | P8 |                                                                 |

|        |          |    |   | D90 | D91 | D92 | D93 | P9 |                                                                 |

|        |          |    |   | PC0 | PC1 | PC2 | PC3 | С  | - 4 column                                                      |

|        |          |    |   |     |     |     |     |    | even parity bits, no<br>row parity bit<br>- C = 0 as a stop bit |

While STATE3 is valid (FOUND command is active), IM283 is ready to provide the 40 bits of the ID data (D00 to D93) to the microcontroller, MSB first.

## 2.2.2 ID transfer protocol

Transfer protocol is described below. For timing characteristics, refer to AC electrical characteristics.

When powered, activation of IM283 will occur only when the host applies high level to ON pin.

The host will turn FL283 in acquisition mode (reading) by applying a RESTART command of the type: low/high/low. All readings should start only after such pulsed reset.

When a tag is read, IM283 returns a FOUND interrupt to the host that can then clock out the 40 ID bits. When done so, next reading will occur only after than a RESTART command is sent.

#### **IMPORTANT NOTES:**

→ When FOUND turns active, the first bit of data is already present on the SDT output pin.

→ Each changing low-to-high level of SCK provides the next bit on SDT.

Only 39 SCK pulses are necessary to clock the 40 ID bits.

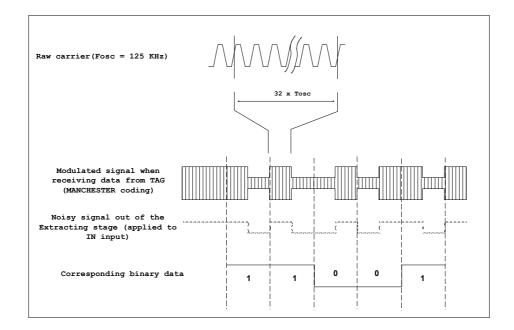

### 2.2.3 Decoding of the input stream

According to Manchester coding the information read out from the tag is modulated as follows:

# 2.2.4 Detailed usage of the pins of IM283

| Pin<br># | Pin Name | I/O Type                                                              | Description                                                                                                                                                                                                                     | NOTE                              |

|----------|----------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1        | INVERT   | CMOS input, pulled up                                                 | High level on the input induces 180° phase between OSC_OUT1 and OSC_OUT2,                                                                                                                                                       | See Table 4 for full description  |

| 2        | WRITE    | CMOS input, pulled down                                               | WRITE and C1 pins control:<br>- READ/WRITE mode<br>- data-rate settings                                                                                                                                                         | See Table 3 for full description  |

| 3        | RESTART  | H-active CMOS<br>input, internally<br>pulled-down                     | A pulse on RESTART pin should occur before any reading cycle.                                                                                                                                                                   |                                   |

| 4        | FOUND    | CMOS Output                                                           | High level on this output indicates that<br>the received ID code is correct and<br>can be read out from microcontroller.                                                                                                        |                                   |

| 5        | SCK      | CMOS I/O<br>(input is pulled-<br>down)                                | Input pin In Read Mode. Each low-to-<br>high transition on SCK (when FOUND<br>is high) puts the next bit of the ID code<br>on the SDT output.<br>Output pin in Write mode                                                       | See Table 3 for full description  |

|          |          |                                                                       | Fc(125kHz) is output on SCK.                                                                                                                                                                                                    |                                   |

| 6        | SDT      | CMOS output                                                           | SDT acts as serial data output for the decoded ID code When FOUND is high, each low to high transition on SCK acts on the SDT pin to output the next bit of the ID code MSB (D00) is sent first (see "Data Transfer Protocol"). | See Table 3 for full description  |

| 7        | C1       | CMOS input, pulled down                                               | WRITE and C1 pins control:<br>- READ/WRITE mode<br>- data-rate settings                                                                                                                                                         | See table 3 for full description. |

| 8        | MS       | H-active CMOS input, pulled up                                        | Three-state control of OSC_OUT1.<br>When high – OSC_OUT1 is in high Z state                                                                                                                                                     | See Table 4 for full description. |

| 9        | GND      |                                                                       | Power supply                                                                                                                                                                                                                    |                                   |

| 10       | DIRECT   | H-active CMOS<br>input, internally<br>pulled down                     | DIRECT should be left unconnected or tied to ZERO).                                                                                                                                                                             | See table 3 for full description. |

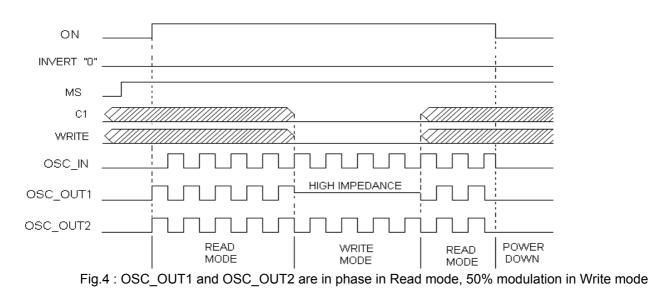

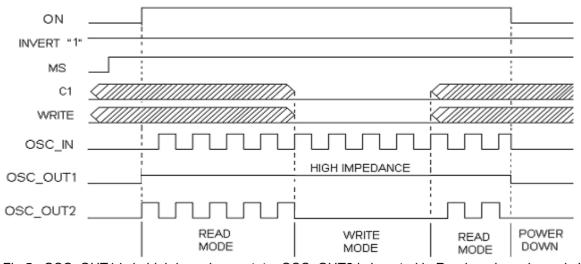

| 11       | C_BYPASS | Application scher<br>Notes: 1. A squ<br>2. Extern<br>3. OSC_<br>shown | nected to RF circuitry:<br>matics are given in Chapter 6. Application<br>are wave CMOS level signal can be appli<br>nal filtering capacitor on C_BYPASS.<br>OUT1 and OSC_OUT2 operating mode<br>0. 2, Fig. 3 and Fig. 4         | ed on OSC_IN also.                |

| 12       | IN       |                                                                       |                                                                                                                                                                                                                                 |                                   |

| 13       | OSC_IN   |                                                                       |                                                                                                                                                                                                                                 |                                   |

| 14       | OSC_OUT2 |                                                                       |                                                                                                                                                                                                                                 |                                   |

| 15       | OSC_OUT1 |                                                                       | When active high the ON significant the                                                                                                                                                                                         |                                   |

| 16       | ON       | H-active CMOS<br>input, internally<br>pulled down                     | When active high, the ON pin turns the circuit into full operation<br>When ON is low, the circuit is turned into sleep, digital part is in reset state.                                                                         |                                   |

| 17       | VDDA     |                                                                       | Analog power supply                                                                                                                                                                                                             |                                   |

# **IM283**

| Pin<br># | Pin Name | I/О Туре | Description          | NOTE |

|----------|----------|----------|----------------------|------|

| 18       | VDD      |          | Digital power supply |      |

Table.3: Read/Write operating modes control and digital signals behaviour

| CONT   | ROL PINS |    | BEHAVIOUR                      |                            |                              |                                                |                                             |  |

|--------|----------|----|--------------------------------|----------------------------|------------------------------|------------------------------------------------|---------------------------------------------|--|

| DIRECT | WRITE    | C1 | OPERATING<br>MODES             | RESTART                    | FOUND                        | SCK                                            | SDT                                         |  |

| 0      | 0        | 0  | WRITE                          | Not used                   | Not used                     | Out:<br>Fc (125kHz)                            | Not used                                    |  |

| 0      | 0        | 1  | READ<br>(data<br>rate=8Kbit/s) | Initiate new<br>read cycle | Interrupt when ID code ready | Input clock to<br>stream-out ID<br>code on SDT | Serial ID code<br>output; clocked<br>by SCK |  |

| 0      | 1        | 0  | READ<br>(data<br>rate=2Kbit/s) | Initiate new<br>read cycle | Interrupt when ID code ready | Input clock to<br>stream-out ID<br>code on SDT | Serial ID code<br>output; clocked<br>by SCK |  |

| 0      | 1        | 1  | READ<br>(data<br>rate=4Kbit/s) | Initiate new<br>read cycle | Interrupt when ID code ready | Input clock to<br>stream-out ID<br>code on SDT | Serial ID code<br>output; clocked<br>by SCK |  |

<u>Application Note for Mode Control Pins</u>: Pins WRITE and C1 are static inputs in case of read-only tags. In case of read-write tags these two inputs (or only one of them) must be controlled dynamically by the host.

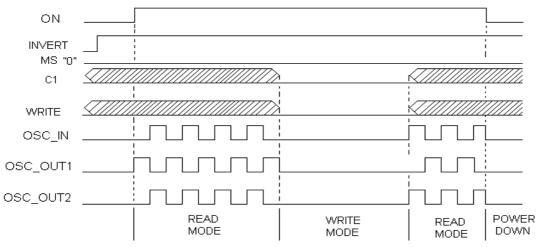

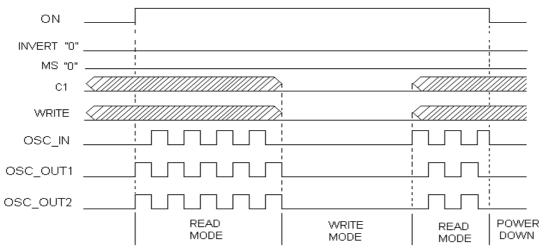

#### Table.4 : Specification of OSC\_OUT1 and OSC\_OUT2 behaviour according to different operating modes

| OPERATING<br>MODE | Pin<br>INVERT | Pin MS<br>(Modulation<br>select) | OSC_OUT1 and OSC_OUT2<br>behaviour             | Shown on<br>Application<br>figure : |

|-------------------|---------------|----------------------------------|------------------------------------------------|-------------------------------------|

| READ              | 0             | Х                                | OSC_OUT1 = not OSC_IN<br>OSC_OUT2 = not OSC_IN | Fig .3/ Fig.4                       |

|                   | 1             | 0                                | OSC_OUT1 = not OSC_IN<br>OSC_OUT2 = OSC_IN     | Fig .2                              |

|                   |               | 1                                | OSC_OUT1="Z"<br>OSC_OUT2 = not OSC_IN          | Fig .5                              |

| WRITE             | 0             | 0                                | OSC_OUT1 = 0<br>OSC_OUT2 = 0                   | Fig .3                              |

|                   |               | 1                                | OSC_OUT1="Z"<br>OSC_OUT2 = not OSC_IN          | Fig .4                              |

|                   | 1             | 0                                | OSC_OUT1 = 0<br>OSC_OUT2 = 0                   | Fig .2                              |

|                   |               | 1                                | OSC_OUT1="Z"<br>OSC_OUT2 = 0                   | Fig .5                              |

Fig.2 : OSC\_OUT1 and OSC\_OUT2 are inverted in Read mode, 100% modulation in Write mode

Fig.3 : OSC\_OUT1 and OSC\_OUT2 are in phase in Read mode, 100% modulation in Write mode

STID MOS

Fig.5 : OSC\_OUT1 is in high impedance state, OSC\_OUT2 is inverted in Read mode and zero in Write mode

# **3 Electrical characteristics**

## 3.1 Absolute Maximum Ratings

| Parameter                                                         | Symbol                            | Conditions                                                 |

|-------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------|

| Max storage temperature                                           | T <sub>STOREmax</sub>             | +150 °C                                                    |

| Min storage temperature                                           | T <sub>STOREmin</sub>             | -65 °C                                                     |

| Power supply voltage                                              | V <sub>DD</sub> &V <sub>DDA</sub> | -0.3 to 7V                                                 |

| Voltage on any inputs                                             |                                   | GND -0.3V to V <sub>DD</sub> +0.3V                         |

| Digital input current                                             | I <sub>IL</sub>                   | $\pm$ 10 mA for Vin <gnd or="" vin="">V<sub>DD</sub></gnd> |

| Analogue input current                                            | I <sub>IA</sub>                   | $\pm 10$ mA for Vin <gnd or="" vin="">V<sub>DD</sub></gnd> |

| Electrostatic discharge according to MIL-<br>STD 883C method 3015 | V <sub>ESD</sub>                  | 750 V                                                      |

Note: Stressed above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified conditions may affect device reliability or cause malfunction.

## 3.2 **Operating Conditions**

| Parameter             | Symbol          | Min | Тур | Max | Units |

|-----------------------|-----------------|-----|-----|-----|-------|

| Operating temperature | T <sub>A</sub>  | -40 |     | +85 | °C    |

| Power supply voltage  | V <sub>DD</sub> | 2.5 |     | 5.5 | V     |

#### 3.3 Timing characteristics

(V\_{DD} = 5 V  $\pm$  5%, T\_A = +27 °C, unless otherwise specified)

| Parameter                                | Symbol               | Test Conditions                         | Min | Тур       | Max | Units |

|------------------------------------------|----------------------|-----------------------------------------|-----|-----------|-----|-------|

| Input pins capacitance                   | Cinp                 |                                         |     |           | 10  | pF    |

| oscillator frequency                     | Fcarrier             | $2.5V \le V_{DD} \le 5.5V$              | 100 | 125       | 150 | kHz   |

| Frame duration<br>(Data Rate = 2Kbit/s): | Tread_2K             | FOSC=125kHz<br>(Data Rate =<br>2Kbit/s) |     | 32.7<br>6 | -   | mS    |

| Frame duration<br>(Data Rate = 4Kbit/s): | Tread_4K             | FOSC=125kHz<br>(Data Rate =<br>4Kbit/s) |     | 16.3<br>8 |     | mS    |

| Frame duration<br>(Data Rate = 8Kbit/s): | Tread_8K             | FOSC=125kHz<br>(Data Rate =<br>8Kbit/s) |     | 8.19      |     | mS    |

| SCK frequency                            | F <sub>SCK</sub>     | Ton and Toff<br>≥100nS                  | 0   |           | 5   | MHz   |

| RESTART pulse length                     | T <sub>RESTART</sub> |                                         | 100 |           |     | ns    |

# 3.4 DC characteristics

| Parameter                   | Symbol          | Test Conditions             | Min                 | Тур | Max                   | Units |

|-----------------------------|-----------------|-----------------------------|---------------------|-----|-----------------------|-------|

| stand-by current            | I <sub>SB</sub> | ON = GND                    |                     |     | 100                   | μA    |

| power consumption           | ICC             |                             |                     |     | 4                     | mA    |

| output leakage current      | I <sub>LO</sub> | Vout=V <sub>DD</sub> or GND |                     |     | 10                    | μA    |

| input low voltage           | V <sub>IL</sub> | digital inputs              | - 0.3               |     | 0.4*V <sub>DD</sub>   | V     |

| input high voltage          | V <sub>IH</sub> | digital inputs              | 0.8*V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 | V     |

| digital output low voltage  | V <sub>OL</sub> | output current=3mA          |                     |     | 0.4                   | V     |

| digital output high voltage | V <sub>OH</sub> | output current=3mA          | 2.6                 |     |                       | V     |

| $(V_{DD} = 4 V \pm 5\%, T_A = +27 \circ C$ | , unless otherwise specified) |

|--------------------------------------------|-------------------------------|

|--------------------------------------------|-------------------------------|

## 3.5 I/O cells

Standard and custom CMOS I/O cells are used in the device.

| Parameter             | Conditions          | Min     | Max  | Units |

|-----------------------|---------------------|---------|------|-------|

| Output HIGH voltage   | I <sub>L=</sub> 4mA | 0.9*VDD |      | V     |

| V <sub>OH</sub>       |                     |         |      |       |

| Output LOW voltage    | I <sub>L=</sub> 4mA |         | 0,5  | V     |

| V <sub>OL</sub>       |                     |         |      |       |

| HIGH level CMOS Input |                     | 0.8*VDD |      | V     |

| voltage               |                     |         |      |       |

| LOW level CMOS Input  |                     |         | 0.4  | V     |

| voltage               |                     |         |      |       |

| Standard Pull-up      |                     | 50      | 100  | [kΩ]  |

| resistor              |                     |         |      |       |

| Standard Pull-down    |                     | 50      | 100  | [kΩ]  |

| resistor              |                     |         |      |       |

| Custom Pull-up        |                     | 370     | 3200 | [kΩ]  |

| Custom Pull-down      |                     | 270     | 4000 | [kΩ]  |

# 4 Application notes

### 4.1 *Low-power application*

Requirements :

Tuning the system: The self-oscillating property of the system requires stable value for coil and tuning capacitor. A ceramic capacitor NPO type or a polyethylene type is recommended

Detection diode: To sustain the voltage on coil a 100 V detection diode is needed. 2 diodes BAV99 in series are recommended.

Other capacitors: Ceramic types are suitable

Decoupling supply: 100nF decoupling supply capacitor is recommended

Interface signals: limitation of clock speed to 5 MHz 100 ns min stable state for all signals

Supply voltage: Depending on application, 3 and 5 V supply is suitable

# 4.1.1 Application Schematics – for 100% Modulation if tag is in read/write mode

| Item | Quantity | Reference | Part   | Power | Tolerance | Voltage | Manufac |

|------|----------|-----------|--------|-------|-----------|---------|---------|

| 1    | 1        | C1        | 4.7n   |       | 10%       | 1000V   |         |

| 2    | 1        | C2        | 100p   |       | 10%       | 63V     |         |

| 3    | 1        | C3        | 3.3n   |       | 10%       | 1000V   |         |

| 4    | 1        | C4,       | 4.7n   |       | 10%       | 1000V   |         |

| 5    | 1        | C5        | 100n   |       | 10%       | 63V     |         |

| 6    | 1        | R1        | 33     |       | 10%       |         |         |

| 7    | 1        | R2        | 220K   |       | 10%       |         |         |

| 8    | 1        | R3        | 330K   |       | 10%       |         |         |

| 9    | 1        | R4        | 100K   |       | 10%       |         |         |

| 10   | 3        | D1,D2,D3  | 1N4148 |       |           |         |         |

| 11   | 1        | L1        | 344uH  |       | 10%       |         |         |

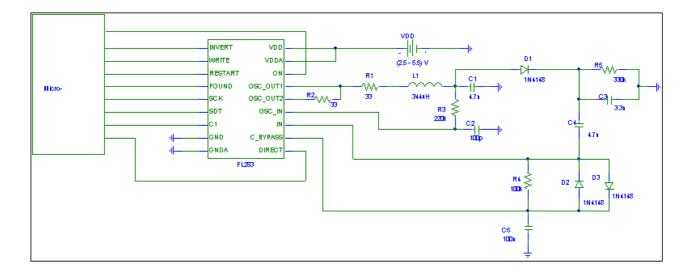

# 4.1.2 Application Schematics – for 50% Modulation if tag is in read/write mode

| ltem | Quantity | Reference | Part   | Power | Tolerance | Voltage | Manufa<br>cturer |

|------|----------|-----------|--------|-------|-----------|---------|------------------|

| 1    | 1        | C1        | 4.7n   |       | 10%       | 1000V   |                  |

| 2    | 1        | C2        | 100p   |       | 10%       | 63V     |                  |

| 3    | 1        | C3        | 3.3n   |       | 10%       | 1000V   |                  |

| 4    | 1        | C4,       | 4.7n   |       | 10%       | 1000V   |                  |

| 5    | 1        | C5        | 100n   |       | 10%       | 63V     |                  |

| 6    | 2        | R1, R2    | 33     |       | 10%       |         |                  |

| 7    | 1        | R4        | 100K   |       | 10%       |         |                  |

| 8    | 1        | R5        | 330K   |       | 10%       |         |                  |

| 9    | 3        | D1,D2,D3  | 1N4148 |       |           |         |                  |

| 10   | 1        | L1        | 344uH  |       | 10%       |         |                  |

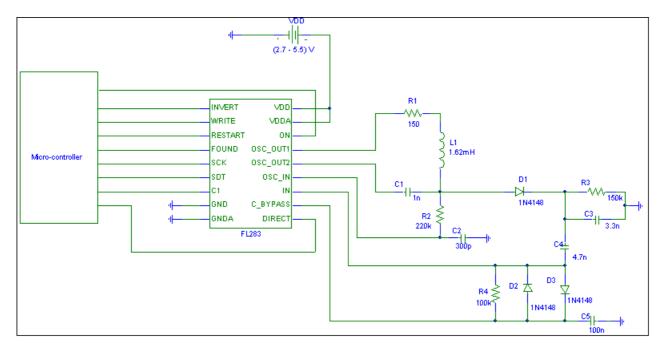

# 4.1.3 Application schematics for read only tags

| ltem | Quantity | Reference | Part   | Power | Tolerance | Voltage | Manufa<br>cturer |

|------|----------|-----------|--------|-------|-----------|---------|------------------|

| 1    | 1        | C1        | 1n     |       | 10%       | 1000V   |                  |

| 2    | 1        | C2        | 300p   |       | 10%       | 63V     |                  |

| 3    | 1        | C3        | 3.3n   |       | 10%       | 1000V   |                  |

| 4    | 1        | C4        | 4.7n   |       | 10%       | 1000V   |                  |

| 5    | 1        | C5        | 100n   |       | 10%       |         |                  |

| 6    | 1        | R1        | 150    |       | 10%       |         |                  |

| 7    | 1        | R2        | 220k   |       | 10%       |         |                  |

| 8    | 1        | R3        | 150K   |       | 10%       |         |                  |

| 9    | 1        | R4        | 100K   |       | 10%       |         |                  |

| 10   | 3        | D1,D2,D3  | 1N4148 |       |           |         |                  |

| 11   | 1        | L1        | 1.62mH |       | 10%       |         |                  |

# 4.1.4 Application schematics for 100% Modulation if tag is in read/write mode

| ltem | Quantity | Reference | Part   | Power | Tolerance | Voltage | Manufa<br>cturer |

|------|----------|-----------|--------|-------|-----------|---------|------------------|

| 1    | 1        | C1        | 1n     |       | 10%       | 1000V   |                  |

| 2    | 1        | C2        | 300p   |       | 10%       | 63V     |                  |

| 3    | 1        | C3        | 3.3n   |       | 10%       | 1000V   |                  |

| 4    | 1        | C4        | 4.7n   |       | 10%       | 1000V   |                  |

| 5    | 1        | C5        | 100n   |       | 10%       |         |                  |

| 6    | 1        | R1        | 150    |       | 10%       |         |                  |

| 7    | 1        | R2        | 220k   |       | 10%       |         |                  |

| 8    | 1        | R3        | 150K   |       | 10%       |         |                  |

| 9    | 2        | R4,R5     | 100K   |       | 10%       |         |                  |

| 10   | 5        | D1÷D5     | 1N4148 |       |           |         |                  |

| 11   | 1        | L1        | 1.62mH |       | 10%       |         |                  |

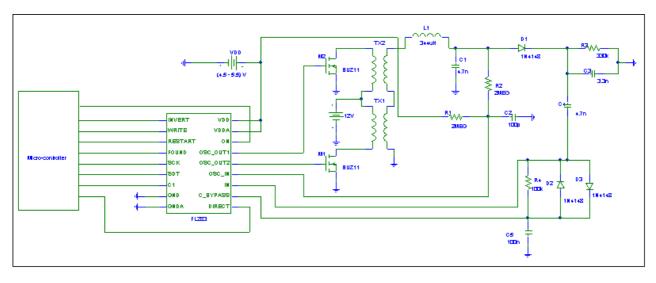

#### 4.2 High Power application

#### Power devices:

High current/low voltage (10A/30V) devices are needed. BUS11 or equivalent are suitable. Due the dissipation of these devices (approximately 1 W per device) a heat sink may be required if the reader is working in permanent mode.

#### □ Transformer

Build in RM ferrite core; each winding is identical (8 turns for each of two primary windings and for the secondary winding.)

#### **u** Tuning of the system:

Stable values for coil and tuning capacitor are required, especially due to the high Q of such an application A low losses polypropylene type capacitor (2000 V) is recommended for C1 to avoid drift generated by high currents in the capacitor

#### Detection diode:

To sustain the voltage on coil, a 2000 V, high-speed detection diode is needed. 3 diodes BA159 in series are recommended.

#### □ Other capacitors:

The 2 capacitors of the RC network (C3 and C4) are 1000V types (polyethylene) Electrolytic types are suitable in other places

#### **Decoupling supply:**

A 4.7uF decoupling capacitor is recommended

#### □ Interface signals:

Limitation of clock speed to 5 MHz 100ns min. stable state for all signals

#### Supply voltage:

5V supply is suitable for IM283A and 12V for the power devices

# 4.2.1 Application schematics for 100% Modulation if tag is in read/write mode

| ltem | Quantity | Reference | Part                                                 | Power | Tolerance | Voltage | Manufactur<br>er                     |

|------|----------|-----------|------------------------------------------------------|-------|-----------|---------|--------------------------------------|

| 1    | 1        | C1        | 4.7n                                                 |       | 10%       | 1000V   |                                      |

| 2    | 1        | C2        | 100p                                                 |       | 10%       | 63V     |                                      |

| 3    | 1        | C3        | 3.3n                                                 |       | 10%       |         |                                      |

| 4    | 1        | C4        | 4.7n                                                 |       | 10%       |         |                                      |

| 5    | 1        | C5        | 100n                                                 |       | 10%       |         |                                      |

| 6    | 2        | R1,R2     | 2MEG                                                 | 0.25W | 10%       |         |                                      |

| 7    | 1        | R3        | 330K                                                 |       | 10%       |         |                                      |

| 8    | 1        | R4        | 100K                                                 |       | 10%       |         |                                      |

| 9    | 3        | D1, D2,D3 | 1N4148                                               |       |           |         |                                      |

| 10   | 1        | L1        | 344uH                                                |       | 10%       |         |                                      |

| 11   | 2        | M1, M2    | BUZ11                                                |       |           |         |                                      |

| 12   | 1        | T1        | RM5-N48/250,<br>3 x 8 turns<br>ø 0.74 coated<br>wire |       |           |         | Siemens,<br>Matsushita<br>Components |

# IM283

# Notes 5

The information in this data sheet is believed to be accurate and reliable. ID MOS reserves the right to make changes without prior notice to any specifications of this product. This device is not intended to be used for systems that support or sustain life or for systems where failure may cause personal injury. The customers use this product at their own risk.