# **Datasheet**

APM32F103xB

Arm® Cortex® -M3 based 32-bit MCU

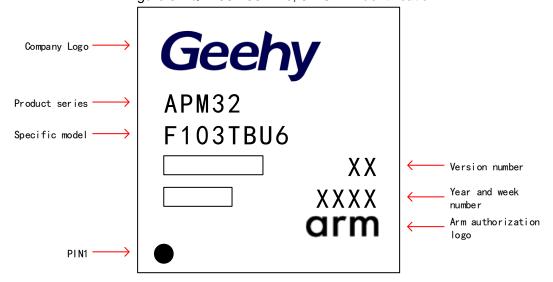

**Chip version: Version E**

Manual version: V 1.1

# 1 Product characteristics

### System and Architecture

- 32-bit Arm® Cortex®-M3 core

- Up to 96MHz working frequency

### Clock and memory

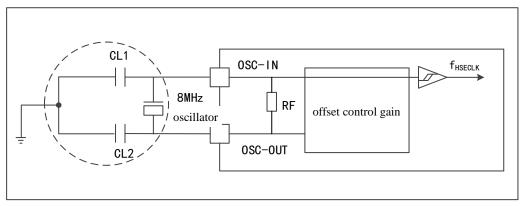

- HSECLK: 4MHz~16 MHz external crystal oscillator supported

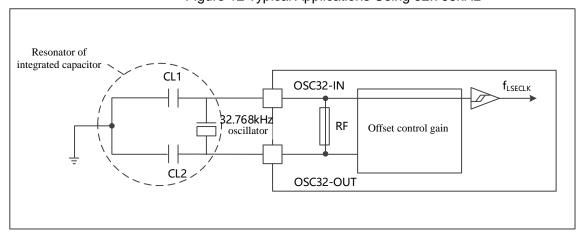

- LSECLK: 32.768KHz crystal/ceramic oscillator supported

- HSICLK: 8MHz RC oscillator calibrated by factory

- LSICLK: 40KHz RC oscillator

- Flash capacity is up to 128KB

- SRAM capacity is up to 36KB

# Power supply and low-power mode

- Reset power supply voltage 2.0V~3.6V

- Programmable voltage detector (PVD) supported

- Sleep, stop and standby three low-power modes supported

- V<sub>BAT</sub> power supply can support RTC and backup register to work

#### ADC and Temperature sensor

- 2 12bit-precision ADC, supporting 16 input channels

- ADC voltage conversion range: 0~V<sub>DDA</sub>

- Support double sampling and holding functions

- 1 internal temperature sensor

#### I/O

- 80/51/37/26 I/O can be selected, which is determined by package model

- All I/O can be mapped to 16 external interrupts

#### DMA

1 DMA, supporting 7 independent configurable channels

#### Timer

- 1 16-bit advanced timer TMR1, which supports dead zone control and emergency braking functions

- 3 16-bit general-purpose timers TMR2/3/4, each with up to 4 independent channels to support input capture, output compare, PWM, pulse count and other functions

- 2 watchdog timers, which are independent IWDT and window WWDT respectively

- 1 24-bit autodecrement system timer SysTick Timer

#### Communication interfaces

- 3 USART, supporting ISO7816, LIN and IrDA functions

- 2 I2C, supporting SMBus/PMBus

- 2 SPI, with up to 18Mbps transmission speed

- 1 QSPI, supporting single-line and four-line access to flash and DMA

- 1 USB 2.0 FS Device

- 2 CAN 2.0B; USBD and CAN can work independently at the same time

#### 1 CRC unit

#### ■ 96-bit UID

# Serial wire debug SWD and JTAG interfaces

#### Chip packaging

- LQFP100/LQFP64/LQFP48/QFN36

#### Applications

Medical devices, PC peripherals, industrial control, smart meters and household appliance

# Contents

| 1     | Product characteristics                    | 1    |

|-------|--------------------------------------------|------|

| 2     | Product information                        | 6    |

| 3     | Pin information                            | 7    |

| 3.1   | Pin distribution                           | 7    |

| 3.2   | Pin function description                   | 9    |

| 4     | Functional Description                     | . 15 |

| 4.1   | System architecture                        | . 16 |

| 4.1.1 | System Block Diagram                       | . 16 |

| 4.1.3 | Address mapping                            | . 17 |

| 4.1.2 | Startup configuration                      | . 18 |

| 4.2   | Core                                       | . 18 |

| 4.3   | Interrupt controller                       | . 18 |

| 4.3.1 | Nested Vector Interrupt Controller (NVIC)  | . 18 |

| 4.3.2 | External Interrupt/Event Controller (EINT) | . 19 |

| 4.4   | Memory                                     | . 19 |

| 4.5   | Clock                                      | . 19 |

| 4.5.1 | Clock tree                                 | . 19 |

| 4.5.2 | Clock and startup                          | . 20 |

| 4.5.3 | RTC and backup register                    | . 21 |

| 4.6   | Power supply and power supply management   | . 21 |

| 4.6.1 | Power supply scheme                        | . 21 |

| 4.6.2 | Voltage regulator                          | . 21 |

| 4.6.3  | Power monitor                                 | 22 |

|--------|-----------------------------------------------|----|

| 4.7    | Low-power mode                                | 22 |

| 4.8    | DMA                                           | 22 |

| 4.9    | GPIO                                          | 22 |

| 4.10   | Communication peripherals                     | 23 |

| 4.10.1 | USART                                         | 23 |

| 4.10.2 | 212C                                          | 23 |

| 4.10.3 | 3 SPI                                         | 23 |

| 4.10.4 | 1QSPI                                         | 23 |

| 4.10.5 | 5 CAN                                         | 23 |

| 4.10.6 | SUSBD                                         | 23 |

| 4.10.7 | 7 Simultaneous use of USBD and CAN interfaces | 24 |

| 4.11   | Analog peripherals                            | 24 |

| 4.11.1 | ADC                                           | 24 |

| 4.12   | SWJ-DP                                        | 24 |

| 4.13   | Timer                                         | 24 |

| 4.14   | WDT                                           | 25 |

| 4.15   | CRC                                           | 26 |

| 5      | Electrical characteristics                    | 26 |

| 5.1    | Test conditions of electrical characteristics | 26 |

| 5.1.1  | Maximum and minimum values                    | 26 |

| 5.1.2  | Typical value                                 | 26 |

| 5.1.3  | Typical curve                                 | 26 |

| 5.1.4  | Power supply scheme                           | 27 |

| 5.1.5 | Load capacitance                                                | 28 |

|-------|-----------------------------------------------------------------|----|

| 5.2   | Test under general operating conditions                         | 28 |

| 5.3   | Absolute maximum rated value                                    | 29 |

| 5.3.1 | Maximum temperature characteristics                             | 29 |

| 5.3.2 | Maximum rated voltage characteristics                           | 29 |

| 5.3.3 | Maximum rated current characteristics                           | 31 |

| 5.3.4 | Electrostatic discharge (ESD)                                   | 31 |

| 5.3.5 | Static latch-up (LU)                                            | 32 |

| 5.4   | Memory                                                          | 32 |

| 5.4.1 | Flash characteristics                                           | 32 |

| 5.5   | Clock                                                           | 33 |

| 5.5.1 | Characteristics of external clock source                        | 33 |

| 5.5.2 | Characteristics of internal clock source                        | 35 |

| 5.5.3 | PLL Characteristics                                             | 36 |

| 5.6   | Power supply and power supply management                        | 36 |

| 5.6.1 | Test of Embedded Reset and Power Control Module Characteristics | 36 |

| 5.7   | Power Consumption                                               | 37 |

| 5.7.1 | Power consumption test environment                              | 37 |

| 5.7.2 | Power consumption in operation mode                             | 38 |

| 5.7.3 | Power consumption in sleep mode                                 | 39 |

| 5.7.4 | Power consumption in stop mode                                  | 40 |

| 5.7.5 | Power consumption in standby mode                               | 40 |

| 5.7.6 | Peripheral power consumption                                    | 41 |

| 5.7.7           | Backup Domain Power Consumption                       | 42                    |

|-----------------|-------------------------------------------------------|-----------------------|

| 5.8             | Wake-up time in low-power mode                        | 42                    |

| 5.9             | I/O port characteristics                              | 42                    |

| 5.10            | NRST pin characteristics                              | 45                    |

| 5.11            | Communication peripherals                             | 46                    |

| 5.11.1          | I2C peripheral characteristics                        | 46                    |

| 5.11.2          | SPI peripheral characteristics                        | 47                    |

| 5.11.3          | USBD peripheral characteristics                       | 50                    |

| 5.12            | Analog peripherals                                    | 52                    |

| 5.12.1          | ADC                                                   | 52                    |

| 5.13            | Temperature sensor characteristics                    | 55                    |

| 6               | Package information                                   | 56                    |

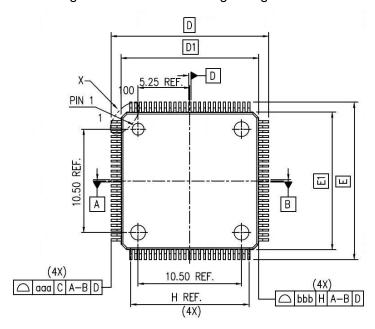

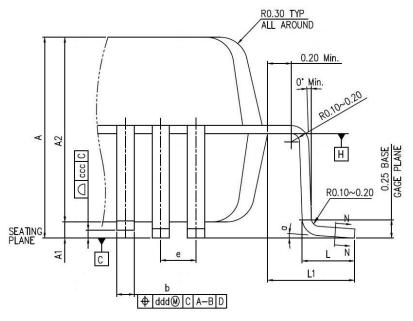

| 6.1             | LQFP100 Package Diagram                               | 56                    |

| 6.2             | LQFP64 Package Diagram                                | 59                    |

| 6.3             | LQFP48 Package Diagram                                | 62                    |

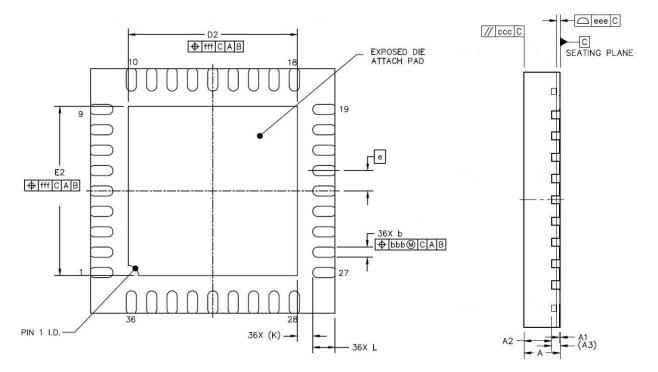

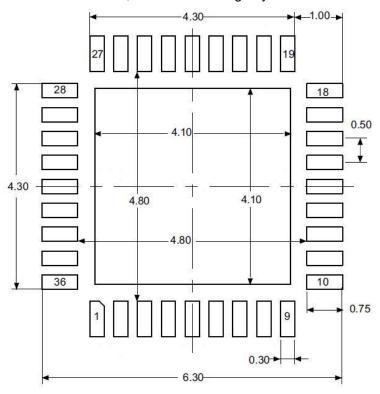

| 6.4             | QFN36 Package Diagram                                 | 65                    |

|                 | QI NOO Fackage Diagram                                | 00                    |

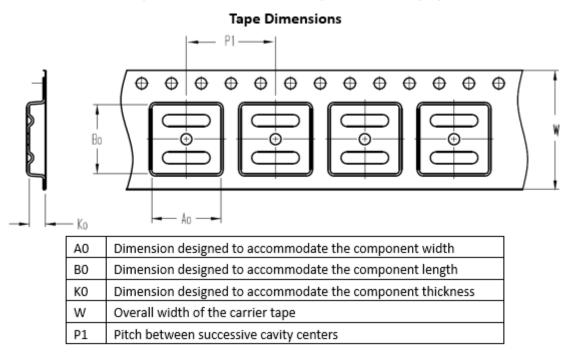

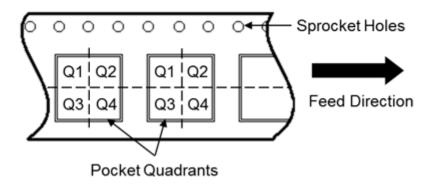

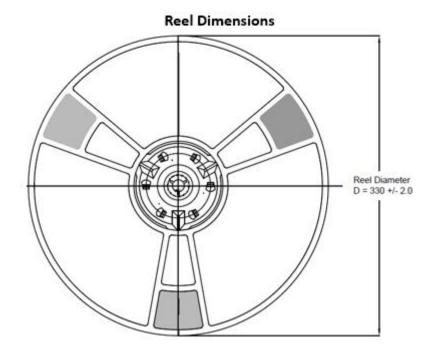

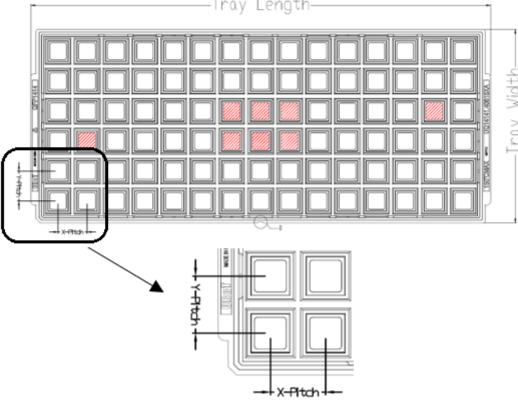

| 7               | Packaging Information                                 |                       |

| <b>7</b><br>7.1 |                                                       | 68                    |

| -               | Packaging Information                                 | <b> 68</b><br>68      |

| 7.1             | Packaging Information                                 | <b>68</b><br>68<br>70 |

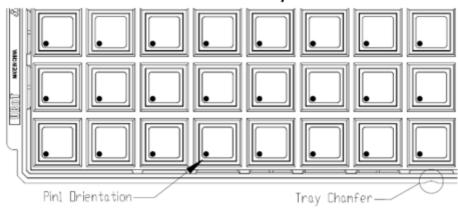

| 7.1<br>7.2      | Packaging Information  Reel Packaging  Tray packaging | <b>68</b><br>68<br>70 |

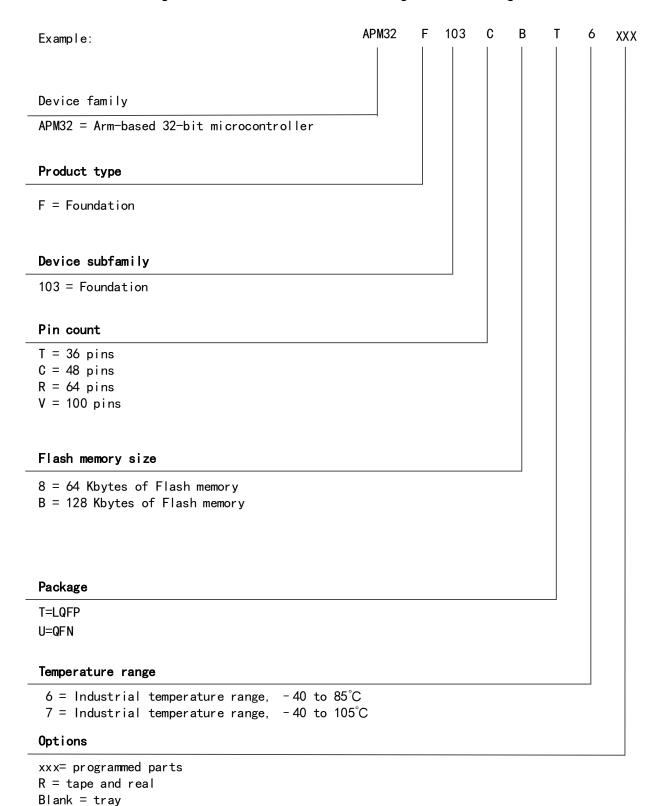

# 2 Product information

See the following table for APM32F103xB product functions and peripheral configuration.

Table1 Functions and Peripherals of APM32F103xB Series Chips

| Р              | roduct               |       |                              |      | APM32         | F103xB   |                              |         |      |  |  |

|----------------|----------------------|-------|------------------------------|------|---------------|----------|------------------------------|---------|------|--|--|

|                | Model                | T8U6  | TBUx                         | C8T6 | CBT6          | R8T6     | RBTx                         | V8T6    | VBT6 |  |  |

| Р              | ackage               | QF    | N36                          | LQI  | LQFP48 LQFP64 |          |                              | LQFP100 |      |  |  |

| Core and maxim | um working frequency |       | Arm® 32-bit Cortex®-M3@96MHz |      |               |          |                              |         |      |  |  |

| Work           | Working voltage      |       |                              |      | 2.0~          | 3.6V     |                              |         |      |  |  |

| Fl             | ash(KB)              | 64    | 128                          | 64   | 128           | 64       | 128                          | 64      | 128  |  |  |

| SF             | RAM(KB)              |       |                              |      | 3             | 6        | •                            |         |      |  |  |

| (              | GPIOs                | 2     | 6                            | ;    | 37            | 5        | 51                           | 8       | 0    |  |  |

|                | USART                | :     | 2                            |      |               | ;        | 3                            |         |      |  |  |

|                | SPI                  |       | 1                            |      | 2             |          |                              |         |      |  |  |

| Communication  | QSPI                 |       |                              |      | 0             |          |                              | 1       |      |  |  |

| interface      | CAN                  |       |                              | 2    |               |          |                              |         |      |  |  |

|                | I2C                  |       | 1                            | 2    |               |          |                              |         |      |  |  |

|                | USBD                 | 1     |                              |      |               |          |                              |         |      |  |  |

|                | 16-bit advanced      | 1     |                              |      |               |          |                              |         |      |  |  |

| Timer          | 16-bit general       |       |                              |      | 3             | 3        |                              |         |      |  |  |

| Timer          | System tick timer    |       |                              | 1    |               |          |                              |         |      |  |  |

|                | Watchdog             |       |                              |      | 2             | 2        |                              |         |      |  |  |

| Real           | -time clock          |       |                              |      | 1             | <u> </u> |                              |         |      |  |  |

| 12-bit ADC     | Unit                 |       |                              |      | 2             | 2        |                              |         |      |  |  |

| 12-DIL ADO     | Number of channels   | 10 16 |                              |      |               |          |                              |         |      |  |  |

| Operatin       | g temperature        |       |                              | -    |               |          | 40°C to 105°<br>-40°C to 125 |         |      |  |  |

Note: When x is 6, ambient temperature is from -40°C to 85°C, and the junction temperature is from -40°C to 105°C; When x is 7, ambient temperature is from -40°C to 105°C, and the junction temperature is from -40°C to 125°C.

# 3 Pin information

# 3.1 Pin distribution

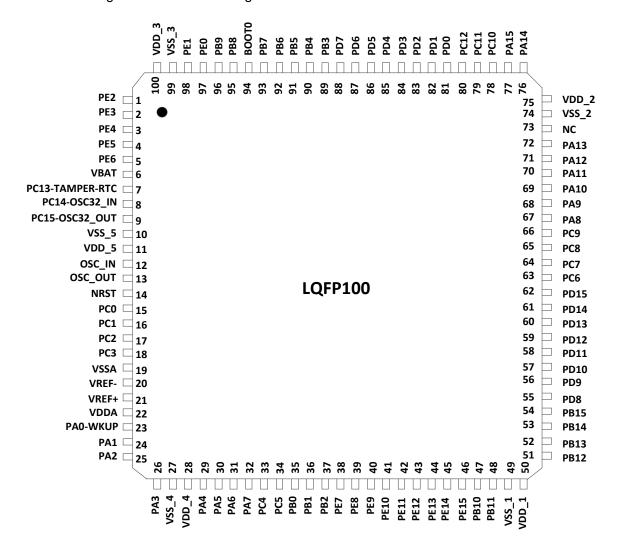

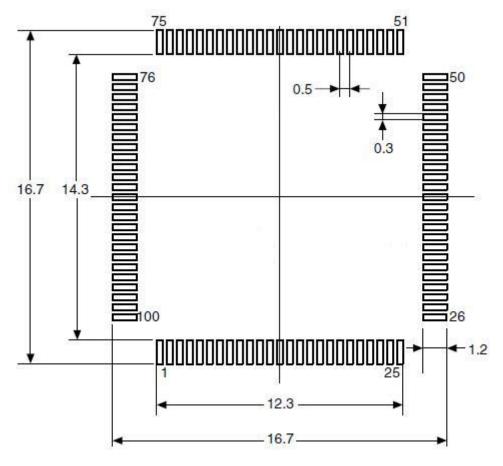

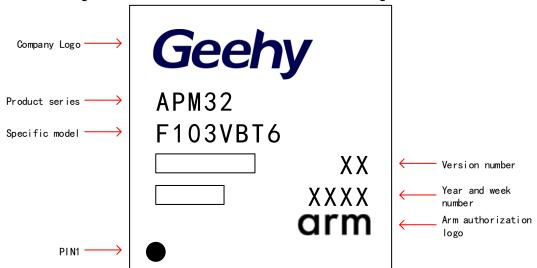

Figure 1 Distribution Diagram of APM32F103xB Series LQFP100 Pins

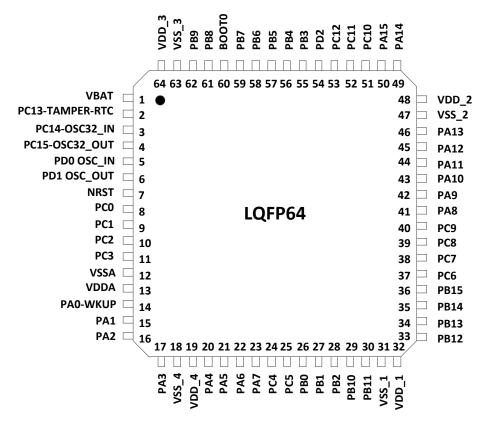

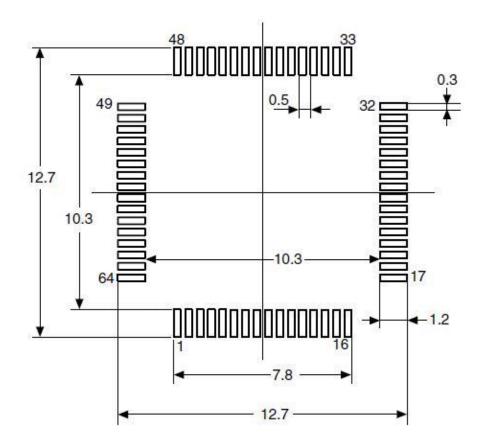

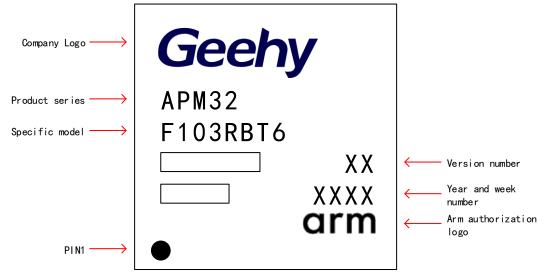

Figure 2 Distribution Diagram of APM32F103xB Series LQFP64 Pins

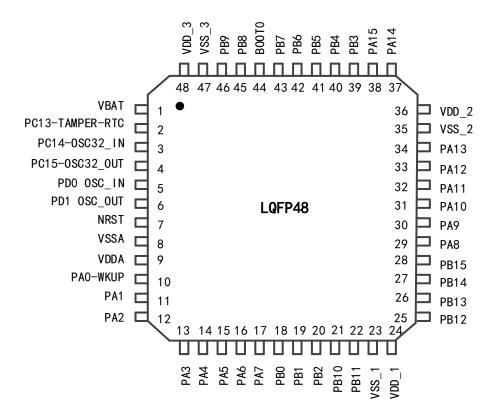

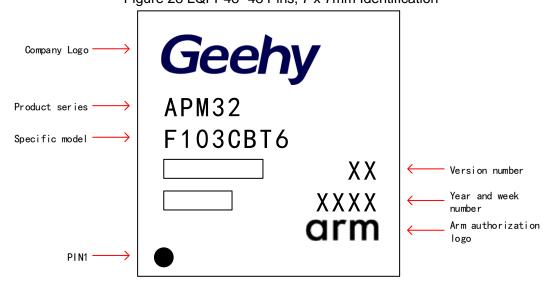

Figure 3 Distribution Diagram of APM32F103xB Series LQFP48 Pins

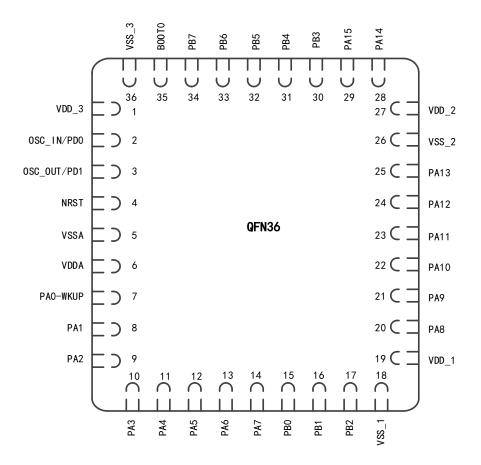

Figure 4 Distribution Diagram of APM32F103xB Series QFN36 Pins

# 3.2 Pin function description

Table2 Legends/Abbreviations Used in Output Pin Table

| N                                                                            | lame      | Abbreviations                                     | Definitions                                                                          |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------|-----------|---------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Din                                                                          | Name      | Unless otherwis                                   | se specified in the bracket below the pin name, the pin functions during and after   |  |  |  |  |  |  |  |  |

| 1 111                                                                        | i Name    |                                                   | reset are the same as the actual pin name                                            |  |  |  |  |  |  |  |  |

|                                                                              |           | S                                                 | Power pin                                                                            |  |  |  |  |  |  |  |  |

| Pi                                                                           | n type    | 1                                                 | Only input pin                                                                       |  |  |  |  |  |  |  |  |

|                                                                              |           | I/O                                               | I/O pin                                                                              |  |  |  |  |  |  |  |  |

|                                                                              |           | FT                                                | FT I/O                                                                               |  |  |  |  |  |  |  |  |

|                                                                              |           | 5Tf                                               | FT I/O, FM+ function                                                                 |  |  |  |  |  |  |  |  |

| 1/0.6                                                                        | structure | STDA 3.3V standard I/O, directly connected to ADC |                                                                                      |  |  |  |  |  |  |  |  |

| 1/0 8                                                                        | structure | STD                                               | 3.3V standard I/O                                                                    |  |  |  |  |  |  |  |  |

|                                                                              |           | BOOT0                                             | Dedicated Boot0 pin                                                                  |  |  |  |  |  |  |  |  |

|                                                                              |           | NRST                                              | Bidirectional reset pin with built-in weak pull-up resistor                          |  |  |  |  |  |  |  |  |

| Ca                                                                           | autions   | Unless other                                      | wise specified in the notes, all I/O is set as floating input during and after reset |  |  |  |  |  |  |  |  |

| Pin Default Select/enable this function directly through peripheral register |           |                                                   |                                                                                      |  |  |  |  |  |  |  |  |

| ı        | lame         | Abbreviations | Definitions                                          |  |  |  |  |  |

|----------|--------------|---------------|------------------------------------------------------|--|--|--|--|--|

| function | multiplexing |               |                                                      |  |  |  |  |  |

|          | function     |               |                                                      |  |  |  |  |  |

|          | Redefining   |               |                                                      |  |  |  |  |  |

|          | function     |               | Select this function through AFIO remapping register |  |  |  |  |  |

### Table3 APM32F103xB Pin Function Description

| Table3 APM32F103xB Pin Function Description  Pin No. Main function (3) Optional multiplexing function |        |        |         |       |      |               |                     |                                |                     |  |  |

|-------------------------------------------------------------------------------------------------------|--------|--------|---------|-------|------|---------------|---------------------|--------------------------------|---------------------|--|--|

|                                                                                                       |        | Pin    | No.     |       |      | (2)           | Main function (3)   | Optional multiplexing function |                     |  |  |

| Pin Name                                                                                              | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type | I/O level (2) | (After reset)       | Default<br>multiplexing        | Redefining function |  |  |

|                                                                                                       | רנ     | ב      | LC      | G     |      | //            |                     | function                       | ranotion            |  |  |

| PE2                                                                                                   | ı      | -      | 1       | -     | I/O  | FT            | PE2                 | TRACECK                        | -                   |  |  |

| PE3                                                                                                   | -      | -      | 2       | -     | I/O  | FT            | PE3                 | TRACED0                        | -                   |  |  |

| PE4                                                                                                   | 1      | 1      | 3       | 1     | 1/0  | FT            | PE4                 | TRACED1                        | •                   |  |  |

| PE5                                                                                                   | 1      | 1      | 4       | 1     | 1/0  | FT            | PE5                 | TRACED2                        | •                   |  |  |

| PE6                                                                                                   | 1      | 1      | 5       | 1     | 1/0  | FT            | PE6                 | TRACED3                        | •                   |  |  |

| V <sub>BAT</sub>                                                                                      | 1      | 1      | 6       |       | S    | -             | V <sub>BAT</sub>    | -                              | -                   |  |  |

| PC13-                                                                                                 | 2      | •      | 7       |       | -/0  |               | PC13 <sup>(3)</sup> | TAMBED DTC                     |                     |  |  |

| TAMPER-RTC(4)                                                                                         | 2      | 2      |         | -     | I/O  | -             | FUIS                | TAMPER-RTC                     | -                   |  |  |

| PC14-                                                                                                 | 3      | 3      | 8       | 1     | I/O  |               | PC14 <sup>(3)</sup> | OSC32_IN                       |                     |  |  |

| OSC32_IN <sup>(4)</sup>                                                                               | 3      | 3      | 0       | _     | 1/0  | _             | 1014.7              | 03032_111                      | _                   |  |  |

| PC15-                                                                                                 | 4      | 4      | 9       | _     | I/O  | _             | PC15 <sup>(3)</sup> | OSC32_OUT                      | _                   |  |  |

| OSC32_OUT <sup>(4)</sup>                                                                              | 7      | 7      | 3       |       | 1/0  | _             | 1015                | 00002_001                      | _                   |  |  |

| Vss_5                                                                                                 | -      | -      | 10      | -     | S    | -             | Vss_5               | -                              | -                   |  |  |

| V <sub>DD_5</sub>                                                                                     | -      | -      | 11      | -     | S    | -             | V <sub>DD_5</sub>   | -                              | -                   |  |  |

| OSC_IN                                                                                                | 5      | 5      | 12      | 2     | I    | -             | OSC_IN              | -                              | PD0 <sup>(5)</sup>  |  |  |

| OSC_OUT                                                                                               | 6      | 6      | 13      | 3     | 0    | -             | OSC_OUT             | -                              | PD1 <sup>(5)</sup>  |  |  |

| NRST                                                                                                  | 7      | 7      | 14      | 4     | I/O  | -             | NRST                | -                              | -                   |  |  |

| PC0                                                                                                   | -      | 8      | 15      | -     | I/O  | -             | PC0                 | ADC12_IN10                     | -                   |  |  |

| PC1                                                                                                   | -      | 9      | 16      | -     | I/O  | -             | PC1                 | ADC12_IN11                     | -                   |  |  |

| PC2                                                                                                   | -      | 10     | 17      | -     | I/O  | -             | PC2                 | ADC12_IN12                     | -                   |  |  |

| PC3                                                                                                   | -      | 11     | 18      | -     | I/O  | -             | PC3                 | ADC12_IN13                     | -                   |  |  |

| Vssa                                                                                                  | 8      | 12     | 19      | 5     | S    | -             | Vssa                | -                              | -                   |  |  |

| V <sub>REF-</sub>                                                                                     | -      | -      | 20      | -     | S    | -             | V <sub>REF</sub> -  | -                              | -                   |  |  |

| V <sub>REF+</sub>                                                                                     | -      | -      | 21      | -     | S    | -             | V <sub>REF</sub> +  | -                              | -                   |  |  |

| V <sub>DDA</sub>                                                                                      | 9      | 13     | 22      | 6     | S    | -             | V <sub>DDA</sub>    | -                              | -                   |  |  |

|                                                                                                       |        |        |         |       |      |               |                     | WKUP/                          |                     |  |  |

| PA0-WKUP                                                                                              | 10     | 14     | 23      | 7     | I/O  | _             | PA0                 | USART2_CTS <sup>(6)</sup> /    | _                   |  |  |

| I AU-WROF                                                                                             | 10     | 14     | 20      | '     | 1/0  | -             | 1 70                | ADC12_IN0/                     | -                   |  |  |

|                                                                                                       |        |        |         |       |      |               |                     | TMR2_CH1_ETR <sup>(6)</sup>    |                     |  |  |

|                                                                                                       |        |        |         |       |      |               |                     | USART2_RTS(6)/                 |                     |  |  |

| PA1                                                                                                   | 11     | 15     | 24      | 8     | I/O  | -             | PA1                 | ADC12_IN1/                     | -                   |  |  |

|                                                                                                       |        |        |         |       |      |               |                     | TMR2_CH2 <sup>(6)</sup>        |                     |  |  |

|                     |        | Pin    | No.     |       |      | <u>(2</u>     | Main function (3) | Optional multiple                     | king function       |

|---------------------|--------|--------|---------|-------|------|---------------|-------------------|---------------------------------------|---------------------|

| <b>D</b> ' <b>N</b> | 8      | 7,     | 8       | 9     | Туре | ()<br>Jej     |                   | Default                               |                     |

| Pin Name            | LQFP48 | LQFP64 | LQFP100 | QFN36 | (1)  | I/O level (2) | (After reset)     | multiplexing<br>function              | Redefining function |

|                     |        |        |         |       |      |               |                   | USART2_TX <sup>(6)</sup> /            |                     |

| PA2                 | 12     | 16     | 25      | 9     | I/O  | -             | PA2               | ADC12_IN2/                            | -                   |

|                     |        |        |         |       |      |               |                   | TMR2_CH3 <sup>(6)</sup>               |                     |

|                     |        |        |         |       |      |               |                   | USART2_RX <sup>(6)</sup> /            |                     |

| PA3                 | 13     | 17     | 26      | 10    | I/O  | -             | PA3               | ADC12_IN3/                            | -                   |

|                     |        |        |         |       |      |               |                   | TMR2_CH4 <sup>(6)</sup>               |                     |

| Vss_4               | -      | 18     | 27      | -     | S    | -             | V <sub>SS_4</sub> | -                                     | -                   |

| V <sub>DD_4</sub>   | -      | 19     | 28      | 1     | S    | -             | $V_{DD\_4}$       | -                                     | -                   |

|                     |        |        |         |       |      |               |                   | SPI1_NSS <sup>(6)</sup> /             |                     |

| PA4                 | 14     | 20     | 29      | 11    | I/O  | -             | PA4               | USART2_CK(6)/                         | -                   |

|                     |        |        |         |       |      |               |                   | ADC12_IN4                             |                     |

| DAF                 | 15     | 21     | 30      | 12    | I/O  |               | DAE               | SPI1_SCK <sup>(6)</sup> /             |                     |

| PA5                 | 15     | 21     | 30      | 12    | 1/0  | _             | PA5               | ADC12_IN5                             | -                   |

|                     |        |        |         |       |      |               |                   | SPI1_MISO(6)/                         |                     |

| PA6                 | 16     | 22     | 31      | 13    | I/O  |               | PA6               | ADC12_IN6/                            | TMR1_BKIN           |

|                     |        |        |         |       |      |               |                   | TMR3_CH1 <sup>(6)</sup>               |                     |

|                     |        |        |         |       |      |               |                   | SPI1_MOSI(6)/                         |                     |

| PA7                 | 17     | 23     | 32      | 14    | I/O  |               | PA7               | ADC12_IN7/                            | TMR1_CH1N           |

|                     |        |        |         |       |      |               |                   | TMR3_CH2 <sup>(6)</sup>               |                     |

| PC4                 | -      | 24     | 33      |       | I/O  | -             | PC4               | ADC12_IN14                            | -                   |

| PC5                 | -      | 25     | 34      | -     | I/O  | -             | PC5               | ADC12_IN15                            | -                   |

| DDO                 | 10     | 26     | 25      | 15    | I/O  |               | DDO               | ADC12_IN8/                            | TMD4 CHON           |

| PB0                 | 18     | 26     | 35      | 15    | 1/0  | -             | PB0               | TMR3_CH3 <sup>(6)</sup>               | TMR1_CH2N           |

| DD4                 | 40     | 07     | 20      | 10    | 1/0  |               | DD4               | ADC12_IN9/                            | TMD4 CHON           |

| PB1                 | 19     | 27     | 36      | 16    | I/O  | _             | PB1               | TMR3_CH4 <sup>(6)</sup>               | TMR1_CH3N           |

| PB2                 | 20     | 28     | 37      | 17    | 1/0  | FT            | PB2/BOOT1         | -                                     | -                   |

| PE7                 | -      | -      | 38      | -     | I/O  | FT            | PE7               | -                                     | TMR1_ETR            |

| PE8                 | -      | -      | 39      | -     | I/O  | FT            | PE8               | -                                     | TMR1_CH1N           |

| PE9                 | -      | -      | 40      | -     | I/O  | FT            | PE9               | -                                     | TMR1_CH1            |

| PE10                | -      | -      | 41      | -     | I/O  | FT            | PE10              | -                                     | TMR1_CH2N           |

| PE11                | -      | ı      | 42      | -     | I/O  | FT            | PE11              | -                                     | TMR1_CH2            |

| PE12                | -      | ı      | 43      | -     | I/O  | FT            | PE12              | -                                     | TMR1_CH3N           |

| PE13                | -      | -      | 44      | -     | I/O  | FT            | PE13              | -                                     | TMR1_CH3            |

| PE14                | -      | ı      | 45      | -     | I/O  | FT            | PE14              | -                                     | TMR1_CH4            |

| PE15                | -      | 1      | 46      | -     | I/O  | FT            | PE15              | -                                     | TMR1_BKIN           |

| PB10                | 21     | 29     | 47      | -     | I/O  | FT            | PB10              | I2C2_SCL/<br>USART3_TX <sup>(6)</sup> | TMR2_CH3            |

| PB11                | 22     | 30     | 48      | -     | I/O  | FT            | PB11              | I2C2_SDA/<br>USART3_RX <sup>(6)</sup> | TMR2_CH4            |

|                          |        | Pin    | No.     |       |                     | <u> </u>      | Main function (3) | Optional multiples                                                                   | ring function               |

|--------------------------|--------|--------|---------|-------|---------------------|---------------|-------------------|--------------------------------------------------------------------------------------|-----------------------------|

| Pin Name                 | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type <sup>(1)</sup> | I/O level (2) | (After reset)     | Default<br>multiplexing<br>function                                                  | Redefining function         |

| Vss_1                    | 23     | 31     | 49      | 18    | S                   | -             | Vss_1             | -                                                                                    | -                           |

| <b>V</b> <sub>DD_1</sub> | 24     | 32     | 50      | 19    | S                   | -             | V <sub>DD_1</sub> | -                                                                                    | -                           |

| PB12                     | 25     | 33     | 51      | -     | I/O                 | FT            | PB12              | SPI2_NSS/ I2C2_SMBAI/ USART3_CK <sup>(6)</sup> / TMR1_BKIN <sup>(6)</sup> )/ CAN2_RX |                             |

| PB13                     | 26     | 34     | 52      | 1     | I/O                 | FT            | PB13              | SPI2_SCK/ USART3_CTS <sup>(6)</sup> / TMR1_CH1N <sup>(6)</sup> / QSPI_IOO/ CAN2_TX   |                             |

| PB14                     | 27     | 35     | 53      | -     | I/O                 | FT            | PB14              | SPI2_MISO/<br>USART3_RTS <sup>(6)</sup> /<br>TMR1_CH2N <sup>(6)</sup> /<br>QSPI_IO1  |                             |

| PB15                     | 28     | 36     | 54      | -     | I/O                 | FT            | PB15              | SPI2_MOSI/<br>TMR1_CH3N <sup>(6)</sup> /<br>QSPI_IO2                                 | -                           |

| PD8                      | -      | -      | 55      | -     | I/O                 | FT            | PD8               | QSPI_IO3                                                                             | USART3_TX                   |

| PD9                      | -      | -      | 56      | -     | I/O                 | FT            | PD9               | -                                                                                    | USART3_RX                   |

| PD10                     | -      | -      | 57      | 1     | I/O                 | FT            | PD10              | QSPI_CLK                                                                             | USART3_CK                   |

| PD11                     | -      | -      | 58      | -     | I/O                 | FT            | PD11              | -                                                                                    | USART3_CT<br>S              |

| PD12                     | -      | -      | 59      | -     | I/O                 | FT            | PD12              | QSPI_SS_N                                                                            | TMR4_CH1/<br>USART3_RT<br>S |

| PD13                     | -      | -      | 60      | -     | I/O                 | FT            | PD13              | -                                                                                    | TMR4_CH2                    |

| PD14                     | -      | -      | 61      | -     | I/O                 | FT            | PD14              | -                                                                                    | TMR4_CH3                    |

| PD15                     | -      | -      | 62      | -     | I/O                 | FT            | PD15              | -                                                                                    | TMR4_CH4                    |

| PC6                      | -      | 37     | 63      | -     | I/O                 | FT            | PC6               | -                                                                                    | TMR3_CH1                    |

| PC7                      | -      | 38     | 64      | -     | I/O                 | FT            | PC7               | -                                                                                    | TMR3_CH2                    |

| PC8                      | -      | 39     | 65      | -     | I/O                 | FT            | PC8               | -                                                                                    | TMR3_CH3                    |

| PC9                      | -      | 40     | 66      | -     | I/O                 | FT            | PC9               | -                                                                                    | TMR3_CH4                    |

| PA8                      | 29     | 41     | 67      | 20    | I/O                 | FT            | PA8               | USART1_CK/<br>TMR1_CH1 <sup>(6)</sup> /<br>MCO                                       | -                           |

| PA9                      | 30     | 42     | 68      | 21    | I/O                 | FT            | PA9               | USART1_TX <sup>(6)</sup> /<br>TMR1_CH2 <sup>(6)</sup>                                | -                           |

|                   |        | Pin    | No.     |       |      | <u> </u>      | Main function (3) | Optional multiples         | king function |      |  |  |  |  |  |  |  |           |

|-------------------|--------|--------|---------|-------|------|---------------|-------------------|----------------------------|---------------|------|--|--|--|--|--|--|--|-----------|

|                   | φ      | 4      | 8       | 9     | Туре | I/O level (2) |                   | Default                    |               |      |  |  |  |  |  |  |  |           |

| Pin Name          | LQFP48 | LQFP64 | LQFP100 | QFN36 | (1)  | <u>e</u>      | (After reset)     | multiplexing               | Redefining    |      |  |  |  |  |  |  |  |           |

|                   | ď      | ΓO     | ΓÖ      | ğ     |      | 0/            |                   | function                   | function      |      |  |  |  |  |  |  |  |           |

| 5440              | 0.4    | 40     |         |       | 1/0  |               | D1.10             | USART1_RX <sup>(6)</sup> / |               |      |  |  |  |  |  |  |  |           |

| PA10              | 31     | 43     | 69      | 22    | I/O  | FT            | PA10              | TMR1_CH3 <sup>(6)</sup>    | -             |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | USART1_CTS/                |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | USBD1DM/                   |               |      |  |  |  |  |  |  |  |           |

| PA11              | 32     | 44     | 70      | 23    | I/O  | FT            | PA11              | USBD2DM/                   | -             |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | CAN1_RX <sup>(6)</sup> /   |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | TMR1_CH4 <sup>(6)</sup>    |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | USART1_RTS/                |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | USBD1DP                    |               |      |  |  |  |  |  |  |  |           |

| PA12              | 33     | 45     | 71      | 24    | I/O  | FT            | PA12              | USBD2DP/                   | -             |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | CAN1_TX <sup>(6)</sup> /   |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   | TMR1_ETR <sup>(6)</sup>    |               |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   |                            |               |      |  |  |  |  |  |  |  |           |

| PA13              | 34     | 46     | 72      | 25    | I/O  | FT            | JTMS/ SWDIO       | -                          | PA13          |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   |                            |               |      |  |  |  |  |  |  |  |           |

| Not connected     | ı      | -      | 73      | -     | -    | -             | -                 | Not connected              | -             |      |  |  |  |  |  |  |  |           |

| Vss_2             | 35     | 47     | 74      | 26    | S    |               | Vss_2             | -                          | -             |      |  |  |  |  |  |  |  |           |

| V <sub>DD_2</sub> | 36     | 48     | 75      | 27    | S    |               | V <sub>DD_2</sub> | -                          | -             |      |  |  |  |  |  |  |  |           |

| PA14              | 37     | 49     | 76      | 28    | I/O  | FT            | JTCK/ SWCLK       | -                          | PA14          |      |  |  |  |  |  |  |  |           |

|                   | 38 50  |        |         |       |      |               |                   |                            |               |      |  |  |  |  |  |  |  | TMR2_CH1_ |

| PA15              |        | 8 50   | 50      | 77    | 29   | I/O           | FT                | JTDI                       | -             | ETR/ |  |  |  |  |  |  |  |           |

| 1 713             | 30     |        | ,,      | 23    | 1/0  | ''            | 0151              | -                          | PA15/         |      |  |  |  |  |  |  |  |           |

|                   |        |        |         |       |      |               |                   |                            | SPI1_NSS      |      |  |  |  |  |  |  |  |           |

| PC10              | -      | 51     | 78      | -     | I/O  | FT            | PC10              | -                          | USART3_TX     |      |  |  |  |  |  |  |  |           |

| PC11              | -      | 52     | 79      | -     | I/O  | FT            | PC11              | -                          | USART3_RX     |      |  |  |  |  |  |  |  |           |

| PC12              | -      | 53     | 80      | -     | I/O  | FT            | PC12              | -                          | USART3_CK     |      |  |  |  |  |  |  |  |           |

| PD0               | -      | -      | 81      | 2     | I/O  | FT            | PD0               | -                          | CAN1_RX       |      |  |  |  |  |  |  |  |           |

| PD1               | -      | -      | 82      | 3     | I/O  | FT            | PD1               | -                          | CAN1_TX       |      |  |  |  |  |  |  |  |           |

| PD2               | -      | 54     | 83      | -     | I/O  | FT            | PD2               | TMR3_ETR                   | -             |      |  |  |  |  |  |  |  |           |

| PD3               | _      | _      | 84      | _     | I/O  | FT            | PD3               | _                          | USART2_CT     |      |  |  |  |  |  |  |  |           |

| FD3               |        | _      | 04      |       | 1/0  | 1 1           | 1 00              |                            | S             |      |  |  |  |  |  |  |  |           |

| PD4               | -      | -      | 85      | 1     | I/O  | FT            | PD4               |                            | USART2_RT     |      |  |  |  |  |  |  |  |           |

| F D 4             |        |        | 00      |       | 1/0  | FI            | F D4              |                            | S             |      |  |  |  |  |  |  |  |           |

| PD5               | -      | -      | 86      | -     | I/O  | FT            | PD5               | -                          | USART2_TX     |      |  |  |  |  |  |  |  |           |

| PD6               | -      | -      | 87      | -     | I/O  | FT            | PD6               | -                          | USART2_RX     |      |  |  |  |  |  |  |  |           |

| PD7               | 1      | -      | 88      | -     | I/O  | FT            | PD7               | -                          | USART2_CK     |      |  |  |  |  |  |  |  |           |

|                   |        | Pin    | No.     |       |                 | 2)            | Main function (3) | Optional multiples                                   | king function                              |

|-------------------|--------|--------|---------|-------|-----------------|---------------|-------------------|------------------------------------------------------|--------------------------------------------|

| Pin Name          | LQFP48 | LQFP64 | LQFP100 | QFN36 | <b>Type</b> (1) | I/O level (2) | (After reset)     | Default<br>multiplexing<br>function                  | Redefining function                        |

| PB3               | 39     | 55     | 89      | 30    | I/O             | FT            | JTDO              | -                                                    | PB3/<br>TRACESWO/<br>TMR2_CH2/<br>SPI1_SCK |

| PB4               | 40     | 56     | 90      | 31    | I/O             | FT            | NJTRST            | -                                                    | PB4/<br>TMR3_CH1/<br>SPI1_MISO             |

| PB5               | 41     | 57     | 91      | 32    | I/O             | -             | PB5               | I2C1_SMBAI                                           | TMR3_CH2/<br>SPI1_MOSI/<br>CAN2_RX         |

| PB6               | 42     | 58     | 92      | 33    | I/O             | FT            | PB6               | I2C1_SCL <sup>(6)</sup> /<br>TMR4_CH1 <sup>(6)</sup> | USART1_TX/<br>CAN2_TX                      |

| PB7               | 43     | 59     | 93      | 34    | I/O             | FT            | PB7               | I2C1_SDA <sup>(6)</sup> /<br>TMR4_CH2 <sup>(6)</sup> | USART1_RX                                  |

| воото             | 44     | 60     | 94      | 35    | I               | -             | BOOT0             | -                                                    | -                                          |

| PB8               | 45     | 61     | 95      | -     | I/O             | FT            | PB8               | TMR4_CH3 <sup>(6)</sup>                              | I2C1_SCL/<br>/CAN1_RX                      |

| PB9               | 46     | 62     | 96      | -     | I/O             | FT            | PB9               | TMR4_CH4 <sup>(6)</sup>                              | I2C1_SDA<br>/CAN1_TX                       |

| PE0               | -      | -      | 97      | -     | I/O             | FT            | PE0               | TMR4_ETR                                             | -                                          |

| PE1               | -      | -      | 98      | -     | I/O             | FT            | PE1               | -                                                    | -                                          |

| Vss_3             | 47     | 63     | 99      | 36    | S               | -             | V <sub>SS_3</sub> | -                                                    | -                                          |

| V <sub>DD_3</sub> | 48     | 64     | 100     | 1     | S               | -             | $V_{DD\_3}$       | -                                                    | -                                          |

- Power supply capacity of PC13, PC14 and PC15 pins is weak. Therefore, there are the following restrictions on these three pins: only one pin can be used as an output at the same time, and can only work in 2MHz mode, the maximum driving load is 30pF, and they cannot be used as a current source (such as driving LED).

- 2. The status of these pins is controlled by the backup area registers (these registers will not be reset by the main reset system).

- 3. For Pin 2 and Pin 3 of QFN36 package, and Pin 5 and Pin 6 of LQFP48 and LQFP64 package, the default configuration after the chip is reset is OSC\_IN and OSC\_OUT function pins, and the software can reset these two pins with PD0 and PD1 functions; for LQFP100 package, PD0 and PD1 are inherent function pins.

- 4. This multiplexing function can be configured to other pins by software (if the corresponding package model has this pin). For details, please refer to the multiplexing function I/O section and debugging setting section of the user manual.

# **4 Functional Description**

This chapter mainly introduces the system architecture, interrupt, on-chip memory, clock, power supply and peripheral features of APM32F103xB series products; for information about the Arm® Cortex®-M3 core, please refer to the Arm® Cortex®-M3 Technical Reference Manual, which can be downloaded from Arm's website.

This version is applicable to APM32F103xB series E version models.

# 4.1 System architecture

# 4.1.1 System Block Diagram

Arm® Cortex®-M3 Bus matrix JTAG/SWD FLASH AHB bus SRAM DMA € CRC QSPI AHB/APB2 bridge AHB/APB1 bridge TMR2/3/4 AF10 RTC EINT WWDT GPIO A/B/C/D/E IWDT ADC1/2 TMR1 SP12 SPI1 USART2/3 USART1 1201 1202 CAN1/CAN2 BAKPR PMU USBD1 (USBD2)

Figure 5 APM32F103xB Series System Block Diagram

- 1. The maximum frequency of AHB and high-speed APB of APM32F103xB series is 96MHz;

- 2. The maximum frequency of low-speed APB of APM32F103xB series is 48MHz.

# 4.1.3 Address mapping

# Table4 Address Mapping Table of APM32F103xB Series

| Region    | Start address | Peripheral name    |

|-----------|---------------|--------------------|

| Code      | 0x0000 0000   | Code mapping area  |

| Code      | 0x0800 0000   | FLASH              |

| Code      | 0x0801 FFFF   | Reserved           |

| Code      | 0x1FFF F000   | System memory area |

| Code      | 0x1FFF F800   | Option byte        |

| Code      | 0x1FFF F80F   | Reserved           |

| SRAM      | 0x2000 0000   | SRAM               |

| APB 1 bus | 0x4000 0000   | TMR2               |

| APB 1 bus | 0x4000 0400   | TMR3               |

| APB 1 bus | 0x4000 0800   | TMR4               |

| APB 1 bus | 0x4000 0C00   | Reserved           |

| APB 1 bus | 0x4000 2800   | RTC                |

| APB 1 bus | 0x4000 2C00   | WWDT               |

| APB 1 bus | 0x4000 3000   | IWDT               |

| APB 1 bus | 0x4000 3400   | Reserved           |

| APB 1 bus | 0x4000 3800   | SPI2               |

| APB 1 bus | 0x4000 3C00   | Reserved           |

| APB 1 bus | 0x4000 4400   | USART2             |

| APB 1 bus | 0x4000 4800   | USART3             |

| APB 1 bus | 0x4000 4C00   | Reserved           |

| APB 1 bus | 0x4000 5400   | I2C1               |

| APB 1 bus | 0x4000 5800   | I2C2               |

| APB 1 bus | 0x4000 5C00   | USBD1(USBD2)       |

| APB 1 bus | 0x4000 6000   | USBD/CAN SRAM      |

| APB 1 bus | 0x4000 6400   | CAN1               |

| APB 1 bus | 0x4000 6800   | CAN2               |

| APB 1 bus | 0x4000 6C00   | BAKPR              |

| APB 1 bus | 0x4000 7000   | PMU                |

| _         | 0x4000 7400   | Reserved           |

| APB2 bus  | 0x4001 0000   | AFIO               |

| APB2 bus  | 0x4001 0400   | EINT               |

| APB2 bus  | 0x4001 0800   | Port A             |

| APB2 bus  | 0x4001 0C00   | Port B             |

| APB2 bus  | 0x4001 1000   | Port C             |

| APB2 bus  | 0x4001 1400   | Port D             |

| Region   | Start address | Peripheral name |

|----------|---------------|-----------------|

| APB2 bus | 0x4001 1800   | Port E          |

| APB2 bus | 0x4001 1C00   | Reserved        |

| APB2 bus | 0x4001 2400   | ADC1            |

| APB2 bus | 0x4001 2800   | ADC2            |

| APB2 bus | 0x4001 2C00   | TMR1            |

| APB2 bus | 0x4001 3000   | SPI1            |

| APB2 bus | 0x4001 3400   | Reserved        |

| APB2 bus | 0x4001 3800   | USART1          |

| APB2 bus | 0x4001 3C00   | Reserved        |

| AHB bus  | 0x4002 0000   | DMA             |

| AHB bus  | 0x4002 0400   | Reserved        |

| AHB bus  | 0x4002 1000   | RCM             |

| AHB bus  | 0x4002 1400   | Reserved        |

| AHB bus  | 0x4002 2000   | Flash interface |

| AHB bus  | 0x4002 2400   | Reserved        |

| AHB bus  | 0x4002 3000   | CRC             |

| AHB bus  | 0x4002 3400   | Reserved        |

| AHB bus  | 0xA000 0000   | QSPI            |

| _        | 0xA000 2000   | Reserved        |

# 4.1.2 Startup configuration

At startup, the user can select one of the following three startup modes by setting the Boot pin:

- Startup from main memory

- Startup from system memory

- Startup from built-in SRAM

Boot loader is stored in the system memory. With it, users can reprogram flash memory through USART1.

#### **4.2** Core

APM32F103xB core is Arm<sup>®</sup> Cortex<sup>®</sup>-M3, with working frequency of 96MHz, compatible with mainstream Arm tools and software.

# 4.3 Interrupt controller

# 4.3.1 Nested Vector Interrupt Controller (NVIC)

It embeds a nested vector interrupt controller (NVIC) and NVIC can handle up to 49 maskable interrupt channels (not including16 interrupt lines of Cortex®-M3) and 16 priority levels. The interrupt vector entry address can be directly transmitted to the core, so that the interrupt response processing with low delay can give priority to the late higher priority interrupt.

# 4.3.2 External Interrupt/Event Controller (EINT)

The external interrupt/event controller consists of 19 edge detectors that generate event/interrupt requests. Its trigger events (rising edge or falling edge or double edge) can be independently configured or shielded; there is a suspend register that maintains the status of all interrupt requests. Up to 80 general-purpose I/O can be connected to 16 external interrupt lines. EINT can detect that the pulse width is less than the clock cycle of the internal APB2.

# 4.4 Memory

The memory includes main memory area, SRAM and information block; the information block includes system memory area and option byte; the system memory area stores BootLoader, 96-bit unique device ID and capacity information of main memory area; the system memory area has been written into the program when leaving the factory and cannot be erased.

Table5

| Memory                  | Maximum<br>bytes | Function                                                                             |  |

|-------------------------|------------------|--------------------------------------------------------------------------------------|--|

| Main memory area        | 128 KB           | Store user programs and data                                                         |  |

| SRAM                    | 36KB             | Can be accessed by byte, half word (16 bits) or word (32 bits).                      |  |

| System memory area 2 KB |                  | Store BootLoader, 96-bit unique device ID, and main memory area capacity information |  |

| Option byte             | 16Bytes          | Configure main memory area read-write protection and MCU working mode                |  |

# 4.5 Clock

#### 4.5.1 Clock tree

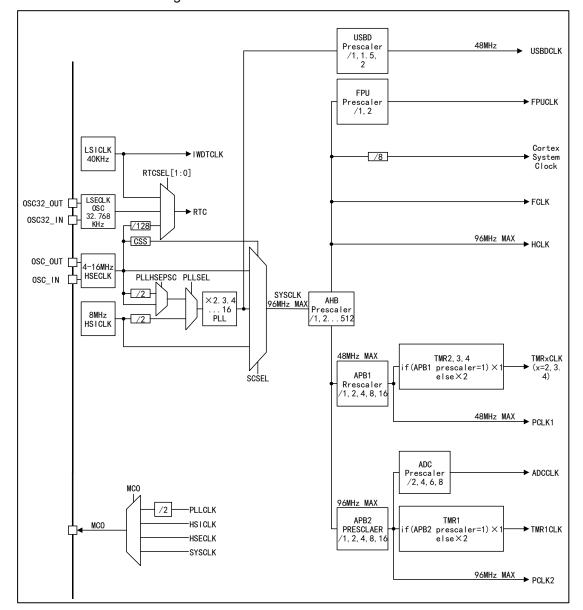

The clock tree of APM32F103xB series is shown in the figure below:

Figure 6 APM32F103xB Series Clock Tree

- 1. The maximum frequency of AHB and high-speed APB of APM32F103xB series is 96MHz;

- 2. The maximum frequency of low-speed APB of APM32F103xB series is 48MHz.

### 4.5.2 Clock and startup

The internal 8MHz RC oscillator is used as the default clock for system startup. It can be switched to an external 4~16MHz clock with failure monitoring through configuration; when an external clock failure is detected, the system will automatically switch to the internal RC oscillator. If an interrupt is set, the software can receive the corresponding interrupt.

The frequency of AHB, high-speed APB (APB2) and low-speed APB (APB1) can be configured by prescaler. The maximum frequency of AHB and high-speed APB is 96MHz, and that of low-speed APB is 48MHz.

For the clock tree of APM32F103xB, refer to Figure 6.

# 4.5.3 RTC and backup register

RTC has a set of continuously running counters, which can provide calendar, alarm interrupt and periodic interrupt functions together with software. Its clock source can be an external 32.768KHz crystal oscillator, an internal 40KHz low-speed RC oscillator or an external high-speed clock with 128 frequency division. In addition, RTC clock error can be calibrated by a 512Hz signal.

Backup register of 10 16-bit registers is used to save 20 bytes of user data when  $V_{DD}$  is disabled.

RTC and backup register are powered by  $V_{DD}$  when  $V_{DD}$  is valid; otherwise, they are powered by  $V_{BAT}$  pin. Reset of system or power reset source and wake-up from standby mode will not cause reset of RTC and backup register.

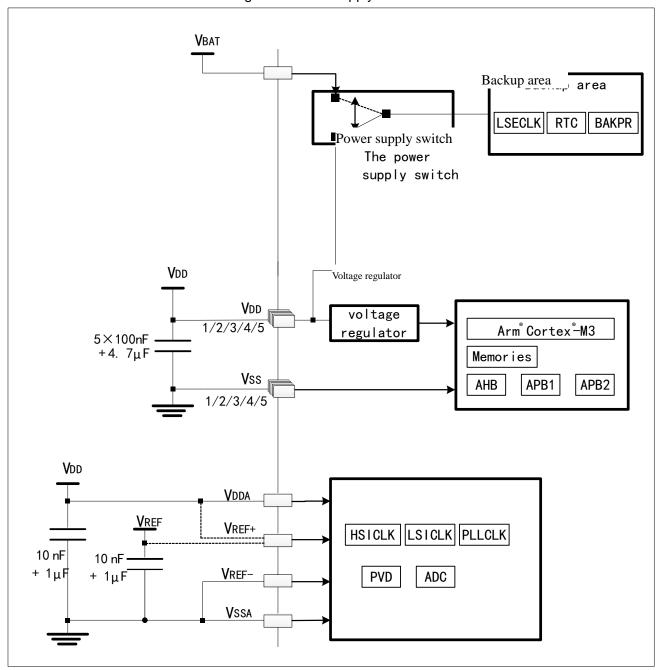

# 4.6 Power supply and power supply management

### 4.6.1 Power supply scheme

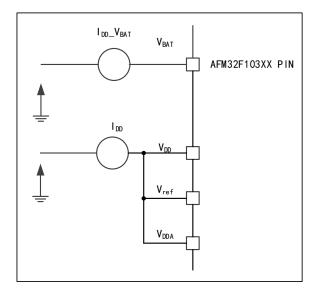

Table6 Power Supply Scheme

| Name             | Voltage range | Description                                                                                 |  |

|------------------|---------------|---------------------------------------------------------------------------------------------|--|

| V                | 2.0 - 2.61/   | V <sub>DD</sub> powers IO interface directly, and powers core circuit through voltage       |  |

| $V_{DD}$         | 2.0∼3.6V      | regulator.                                                                                  |  |

|                  |               | It is connected to V <sub>DD</sub> , and supplies power to ADC, reset module, RC oscillator |  |

| $V_{DDA}$        | 2.4~3.6V      | and PLL analog part. When ADC is used, VDDA is greater than or equal ato 2.4V.              |  |

|                  |               | $V_{DDA}$ and $V_{SSA}$ should be connected to $V_{DD}$ and $V_{SS}$ respectively.          |  |

| \/               | 1.0 - 2.6\/   | When $V_{\text{DD}}$ is disabled, RTC, external 32KHz oscillator and backup register are    |  |

| V <sub>BAT</sub> | 1.8~3.6V      | powered automatically.                                                                      |  |

Note: See Figure 7 Power Supply Scheme for more detailed information about how to connect the power pins

#### 4.6.2 Voltage regulator

The working mode of MCU can be adjusted through voltage regulator so as to reduce power consumption. It mainly has three working modes.

Table7 Operating Mode of Voltage Regulator

| Name                 | Description                                                                                   |  |

|----------------------|-----------------------------------------------------------------------------------------------|--|

| Main mode (MR)       | Provide 1.6 power supply (core, memory and peripheral) in normal power mode.                  |  |

| Low-power mode (LPR) | Provide 1.6V power supply in low-power mode, to save the content of register and SRAM.        |  |

| Power-down mode      | Used in the standby mode of CPU; the voltage regulator stops power supply, and except for the |  |

|                      | standby circuit and backup area, all contents of registers and SRAM will be lost.             |  |

Note: The voltage regulator is always in working state after reset, and outputs with high impedance in power-down mode.

#### 4.6.3 Power monitor

Power-on reset (POR) and power-down reset (PDR) circuits are integrated inside the product. When  $V_{DD}$  reaches the set threshold  $V_{POR/PDR}$ , the system works normally; when the  $V_{DD}$  is lower than the set threshold  $V_{POR/PDR}$ , the system will remain in the reset state without connecting the external reset circuit.

# 4.7 Low-power mode

The product supports three low-power modes. Users can switch between these modes by setting.

Table8 Low-power Mode

| Mode       | Description                                                                                  |

|------------|----------------------------------------------------------------------------------------------|

| Sloop mode | In sleep mode, all peripherals are in working status, but the CPU stops working. If an       |

| Sleep mode | interrupt/event occurs, the CPU will be waked up.                                            |

|            | The stop mode is the mode that can achieve the lowest power consumption without losing       |

|            | the content of SRAM and register. At this time, internal 1.6V power supply stops, causing    |

| Stop mode  | the HSECLK, HSICLK and PLL clocks to turn off, and the voltage regulator is set to the       |

| Stop mode  | normal mode or low-power mode. Interrupt and event wake-up configured as EINT can            |

|            | wake the CPU from the stop mode. EINT signal includes 16 external I/O ports, PVD             |

|            | output, RTC alarm or USBD wake-up signal.                                                    |

|            | The standby mode is the lowest-power mode used by the chip. At this time, the internal       |

|            | voltage regulator is disabled, causing power supply of the internal 1.6V part to be cut off; |

| Standby    | HSECLK, HSICLK and PLL clocks are disabled; the content of SRAM and register will            |

| mode       | disappear. However, the content of the backup register will remain and the standby circuit   |

| mode       | will still work.                                                                             |

|            | The external reset signal on NRST, IWDT reset, a rising edge on WKUP pin or RTC alarm        |

|            | will terminate the standby mode of the chip.                                                 |

Note: When entering the stop or standby mode, RTC, IWDT and corresponding clock will not stop, and the interrupt of QSPI cannot wake up the low power.

#### 4.8 DMA

The product has 7-channel general-purpose DMA, which can manage the data transmission from memory to memory, device to memory, and memory to device.

Each channel has hardware DMA request logic, and the source address, destination address and transmission length of each channel can be set separately by software.

DMA can be used for main peripherals: SPI, I2C, USART, timer TMRx and ADC, QSPI.

#### 4.9 **GPIO**

The product can have up to 80 GPIO pins. Every pin can be switched between input (pull-up, pull-down), output (push-pull, open-drain) or multiplexing functions through software configuration. Most GPIO pins are shared with multiplexed peripherals. To avoid accidental writing of I/O registers, the peripheral functions of I/O pins can be locked by specific

operations.

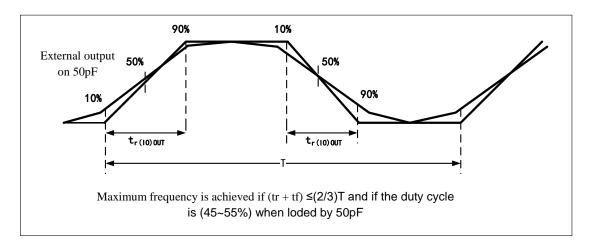

I/O pin turnover speed on the APB2 can reach 18MHz.

# 4.10 Communication peripherals

#### 4.10.1 USART

Three USART communication interfaces are embedded. Among them, the USART1 interface can support the communication rate of 4.5Mbit/s, and the other interfaces support the communication rate of 2.25Mbit/s. It has hardware signal CTS and RTS, compatible with ISO7816 smart card, supports IrDA SIR ENDEC transmission encoding and decoding, and provides LIN master/slave mode.

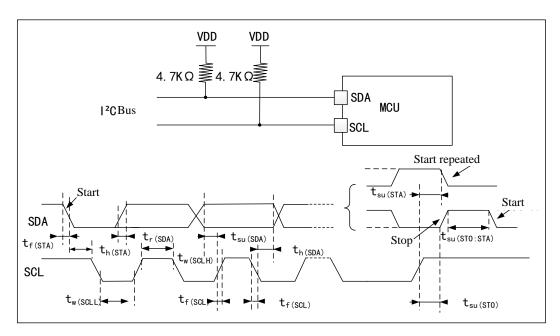

#### 4.10.2 I2C

I2C1/2 can work in multi-master mode or slave mode and support 7-bit and 10-bit addressing. The protocol supports standard and fast modes. Built-in hardware CRC generator/calibrator. DMA operation can be used and SMBus bus version 2.0/PMBus bus is supported.

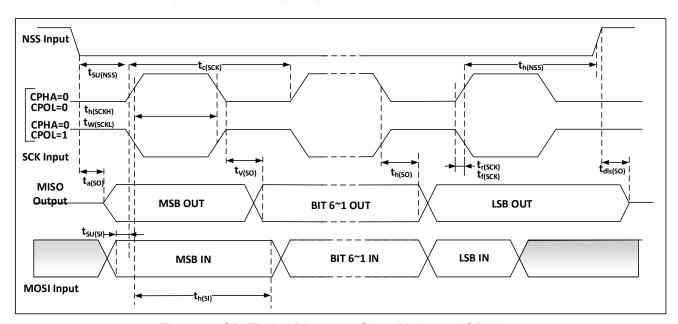

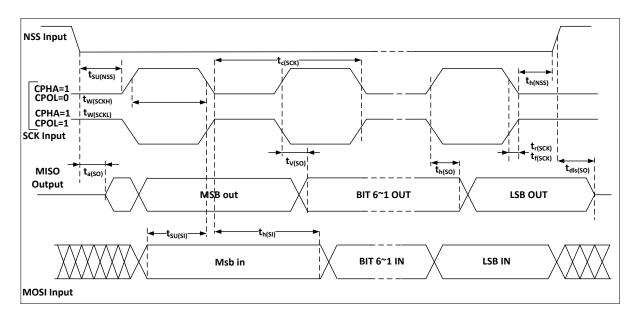

#### 4.10.3 SPI

Two SPI interfaces are embedded, supporting the chip to communicate with external devices in half/full duplex serial mode. It can be configured as master mode or slave mode, with 8 or 16 bits per frame. The communication rate in full-duplex and half-duplex mode can be 18 Mbit/s. All SPI interfaces support DMA operation.

# 4.10.4 QSPI

1 QSPI special communication interface is embedded, which can connect external flash through single-line, double-line or four-line SPI mode, and support 8-bit, 16-bit and 32-bit access. There are 8-byte transmit FIFO and 8-byte receive FIFO inside. DMA operation is supported.

#### 4.10.5 CAN

2 built-in CAN bus interfaces (CAN1 and CAN2 can be used at the same time), compatible with 2.0A and 2.0B (active) specifications, which can communicate at a rate of up to 1Mbit/s. Support standard frame with 11-bit identifier and extended frame with 29-bit identifier, and have 3 transmitting mailboxes and 2 receiving FIFO, and 14 3-level adjustable filters.

#### 4.10.6 USBD

The product embeds USBD modules (USBD1 and USBD2) compatible with full-speed USBD devices, which comply with the standard of full-speed USBD devices (12Mb/s), and the endpoints can be configured by software, and have standby/wake-up functions. The dedicated 48MHz clock for USBD is directly generated by internal PLL. When using the USBD function, the system clock can only be one of 48MHz, 72MHz and 96MHz, which can obtain 48MHz required for USBD through 1 divided frequency, 1.5 fractional frequency, and 2 fractional frequency respectively.

USBD1 and USBD2 share register address and pin interface, so only one of them can be used at the same time.

#### 4.10.7 Simultaneous use of USBD and CAN interfaces

When USBD and CAN are used at the same time, you need to:

- Write 0x00000001 at the base address offset 0x100 of USBD.

- PA11 and PA12 pins are for USBD, and CAN is used to multiplex other pins.

# 4.11 Analog peripherals

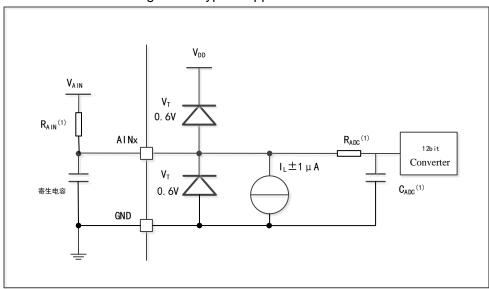

#### 4.11.1 ADC

2 built-in ADCs with 12-bit accuracy, up to 16 external channels; each ADC can realize the conversion between single mode and scanning mode. It can support DMA operation and liberate the CPU. ADC interface supports single sampling, synchronous sampling and holding, and cross sampling and holding logic functions. The analog watchdog function can monitor multiple channels and generate an interrupt when the monitored signal exceeds the preset value.

The timer can be used to synchronize the analog-to-digital conversion with the clock.

#### 4.11.1.1 Temperature sensor

An embedded temperature sensor connected to ADC1\_IN16 input channel can convert the ambient temperature of the chip into digital signal.

#### 4.12 SWJ-DP

The product supports serial debugging interface (SW-DP) and JTAG (JTAG-DP) debugging interface.

JTAG interface provides 5-pin standard JTAG interface for AHB access port.

SW-DP interface provides 2-pin (data + clock) interface for AHB module. Among them, some of 2 pins of SW-DP interface and 5 pins of JTAG interface are multiplexed.

### **4.13** Timer

The product includes 1 advanced-control timer (TMR1), 3 general-purpose timers (TMR2/3/4) and 1 system tick timer.

The following table compares the functions of advanced timer and general-purpose timer:

**Table9 Function Comparison of Timers**

| Timer type         | System tick timer | General-purpose timer  TMR2 TMR3 TMR4 |  | e timer | Advanced timer    |

|--------------------|-------------------|---------------------------------------|--|---------|-------------------|

| Timer name         | Sys Tick Timer    |                                       |  | TMR4    | TMR1              |

| Counter resolution | 24 bits           | 16 bits Up, down, up/down             |  |         | 16 bits           |

| Counter type       | Down              |                                       |  | own     | Up, down, up/down |

| Timer type System tick timer |                                                                                                                                                                                                                              | General-purpose timer                                                                                                                                                                                                                                                                                                                     | Advanced timer                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prescaler factor             | -                                                                                                                                                                                                                            | Any integer between 1 and 65536                                                                                                                                                                                                                                                                                                           | Any integer between 1 and 65536                                                                                                                                                                                                                                                                                                                                                                                          |

| Generate DMA request         | -                                                                                                                                                                                                                            | Yes                                                                                                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Capture/compar<br>e register | -                                                                                                                                                                                                                            | 4                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Complementary output         | -                                                                                                                                                                                                                            | None                                                                                                                                                                                                                                                                                                                                      | Yes                                                                                                                                                                                                                                                                                                                                                                                                                      |