# MGC3130

### Single-Zone 3D Tracking and Gesture Controller Data Sheet

#### Introduction:

The MGC3130 is a three-dimensional (3D) gesture recognition and tracking controller chip based on Microchip's patented GestIC® technology. It enables user command input with natural hand and finger movements. Utilizing the principles of electrical nearfield sensing, the MGC3130 contains all the building blocks to develop robust 3D input sensing systems. low-power Implemented as а mixed-signal configurable controller, it provides a large set of smart functional features with integrated signal driver, a frequency adaptive input path for automatic noise suppression and a digital signal processing unit. Microchip's on-chip Colibri Suite minimizes processing needs, reduces system power consumption and results in low software development efforts for fast time-tomarket success. The MGC3130 is a unique solution that provides gesture information as well as positional data of the human hand in real time and allows realization of a new generation of user interfaces across various industries.

#### Applications:

- Displays

- · Notebooks/Keyboards/PC Peripherals

- Mobile Phones

- Tablet Computers

- Electronic Readers

- · Remote Controls

- · Game Controllers

#### **Power Features:**

- Variety of Several Power Operation modes include:

- Processing mode: 20 mA @ 3.3V, typical

- Programmable Self Wake-up: 110 μA @ 3.3V

- Deep Sleep: 9 µA @ 3.3V, typical

#### **Key Features:**

- Recognition of 3D Hand Gestures and x, y, z Positional Data

- · Proximity and Touch Sensing Capabilities

- · Built-in Colibri Gesture Suite

- · Advanced 3D Signal Processing Unit

- · Detection Range: 0 to 15 cm

- · Receiver Sensitivity: <1 fF

- · Position Rate: 200 positions/sec

- Spatial Resolution: up to 150 dpi

- · Carrier Frequency: 44 kHz to 115 kHz

- · Channels Supported:

- Five receive (Rx) channels

- One transmit (Tx) channel

- · On-chip Auto Calibration

- Low Noise Radiation due to Low Transmit Voltage and Slew Rate Control

- · Noise Susceptibility Reduction:

- On-chip analog filtering

- On-chip digital filtering

- Automatic frequency hopping

- Enables the use of Low-Cost Electrode Material including:

- Printed circuit board

- Conductive paint

- Conductive foil

- Laser Direct Structuring (LDS)

- Touch panel ITO structures

- · Field Upgrade Capability

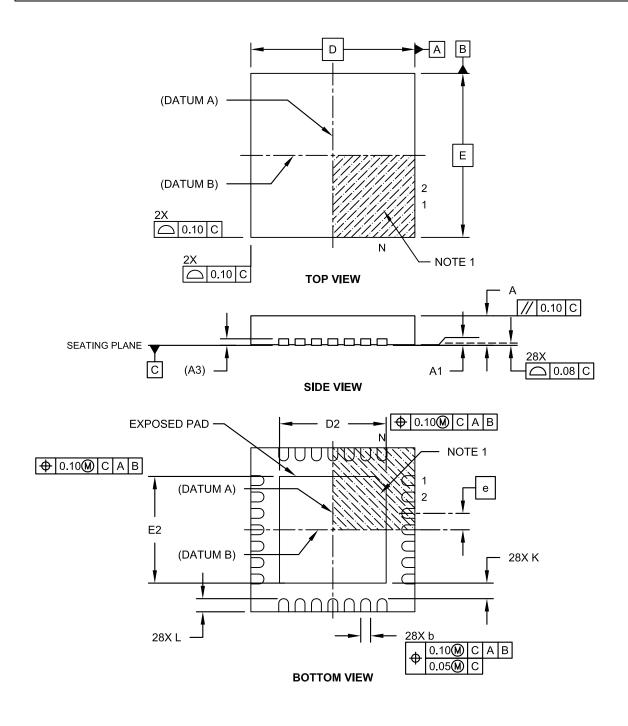

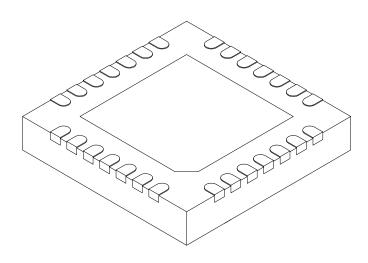

- Small Outline, 28-lead QFN package, 5x5 mm

- Operating Voltage: 2.5V to 3.465V (single supply)

- Temperature Range: -20°C to +85°C

#### **Peripheral Features:**

- 2x I<sup>2</sup>C<sup>™</sup> or SPI Interface for Configuration and Streaming of Positional and Gesture Data

- Multi-zone Support via Master/Slave Architecture

#### **Package Type**

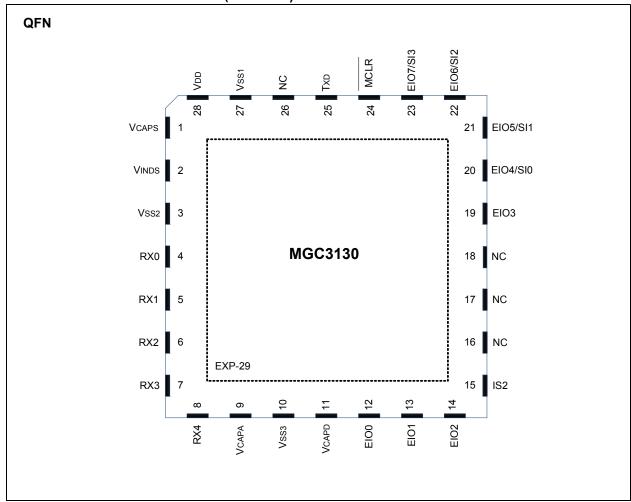

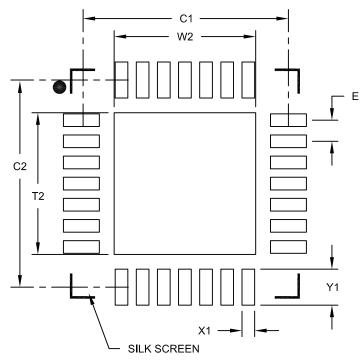

The device is available in 28-lead QFN packaging (see Figure 1).

FIGURE 1: 28-PIN DIAGRAM (MGC3130)

DS40001667C-page 2

TABLE 1: 28-PIN QFN PINOUT DESCRIPTION

| Converter (optional).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17(322 11 | BLE 1: 28-PIN QFN PINOUT DESCRIPTION |          |             |                                                                                                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Converter (optional).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin Name  |                                      | Pin Type | Buffer Type | Description                                                                                                                                                |  |

| STEP-UP converter usage (optional).   STEP-UP converter usage (optional).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VCAPS     | 1                                    | Р        | _           | External filter capacitor (10 $\mu$ F) connection for internal STEP-UP converter (optional).                                                               |  |

| RX0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VINDS     | 2                                    | Р        | _           | External inductor (4.7 µH) + Schottky diode connection for internal STEP-UP converter usage (optional).                                                    |  |

| RX1         5         I         Analog           RX2         6         I         Analog           RX3         7         I         Analog           RX4         8         I         Analog           VCAPA         9         P         —         External filter capacitor (4.7 μF) connection for internal analog voltage regulator (3V).           VSS3         10         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VSEQ         11         P         —         Common ground reference for analog and digital domain.           VEAD         12         I/O         ST         Extended IOO (EIOO)/Transfer Status (TS). TS Internal filter capacitor (4.7 μF) connection for internal digital domain. <td>Vss2</td> <td>3</td> <td>Р</td> <td>_</td> <td>Ground reference for the STEP-UP converter.</td> | Vss2      | 3                                    | Р        | _           | Ground reference for the STEP-UP converter.                                                                                                                |  |

| RX2         6         I         Analog         External filter capacitor (4.7 μF) connection for internal analog voltage regulator (3V).         VSS3         10         P         —         Common ground reference for analog and digital domain.         VCAPD         11         P         —         Common ground reference for analog and digital domain.         VCAPD         VCAPD         11         P         —         Common ground reference for analog and digital domain.         VCAPD         VCAPD         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         External filter capacitor (4.7 μF) connection for internal digital voltage regulator (1.8V).           EIO0         12         I/O         ST         Extended IO0 (EIO0)/Transfer Status (TS). TS in the requires an external 1.8 kΩ pull-up.           EIO2         14         I/O         ST         Extended IO3 (EIO2      | RX0       | 4                                    | I        | Analog      |                                                                                                                                                            |  |

| RX3         7         I         Analog           RX4         8         I         Analog           VCAPA         9         P         —         External filter capacitor (4.7 μF) connection for internal analog voltage regulator (3V).           VSS3         10         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         External filter capacitor (4.7 μF) connection for internal digital voltage regulator (1.8V).           EIO0         12         I/O         ST         Extended IO0 (EIO0)/Transfer Status (TS). TS line requires external 10 kΩ pull-up.           EIO1         13         I/O         ST         Extended IO1 (EIO1)/Interface Selection Pin 1 (IS1).           EIO2         14         I/O         ST         Extended IO2 (EIO2)/IRQ0.           IS2         15         I         ST         Interface Selection Pin 2 (IS2).           NC         16         —         —         Reserved: do not connect.           NC         17         —         —         Reserved: do not connect.           NC         18         —         —         Reserved: do not connect.           EIO3         19         I/O         ST         Extended IO3 (EIO3)/IRQ1/ISQ1/ISQ1/ISQ1/ISQ1/ISQ1/ISQ1/ISQ1                                                                                                                    | RX1       | 5                                    | I        | Analog      |                                                                                                                                                            |  |

| RX4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RX2       | 6                                    | I        | Analog      | Analog input channels: Receive electrode connection.                                                                                                       |  |

| VCAPA   9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RX3       | 7                                    | I        | Analog      |                                                                                                                                                            |  |

| VSS3         10         P         —         Common ground reference for analog and digital domain.           VCAPD         11         P         —         External filter capacitor (4.7 μF) connection for internal digital voltage regulator (1.8 V).           EIO0         12         I/O         ST         Extended IO0 (EIO0)/Transfer Status (TS). TS line requires external 10 kΩ pull-up.           EIO1         13         I/O         ST         Extended IO1 (EIO1)/Interface Selection Pin 1 (IS1).           EIO2         14         I/O         ST         Extended IO2 (EIO2)/IRQ0.           IS2         15         I         ST         Interface Selection Pin 2 (IS2).           NC         16         —         —         Reserved: do not connect.           NC         17         —         —         Reserved: do not connect.           NC         17         —         —         Reserved: do not connect.           NC         18         —         —         Reserved: do not connect.                                                                                                                                                                  | RX4       | 8                                    | I        | Analog      |                                                                                                                                                            |  |

| VCAPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCAPA     | 9                                    | Р        | _           |                                                                                                                                                            |  |

| Voltage regulator (1.8V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Vss3      | 10                                   | Р        | _           | Common ground reference for analog and digital domain.                                                                                                     |  |

| EIO1   13   I/O   ST   Extended IO1 (EIO1)/Interface Selection Pin 1 (IS1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VCAPD     | 11                                   | Р        | _           |                                                                                                                                                            |  |

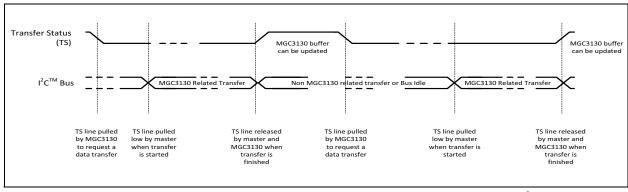

| EIO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EIO0      | 12                                   | I/O      | ST          | ` ,                                                                                                                                                        |  |

| IS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EIO1      | 13                                   | I/O      | ST          | Extended IO1 (EIO1)/Interface Selection Pin 1 (IS1).                                                                                                       |  |

| NC         16         —         Reserved: do not connect.           NC         17         —         —         Reserved: do not connect.           NC         18         —         —         Reserved: do not connect.           EIO3         19         I/O         ST         Extended IO3 (EIO3)/IRQ1/SYNC.           EIO4/SI0         20         I/O         ST         Extended IO4 (EIO4)/Serial Interface 0 (SI0): I²C™_SDA0/SPI_MISO. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           EIO5/SI1         21         I/O         ST         Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           EIO6/SI2         22         I/O         ST         Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           EIO7/SI3         23         I/O         ST         Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           MCLR         24         I/P         ST         Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.           TXD         25         O         Analog         Transmit electrode connection.           NC         26         —         —    | EIO2      | 14                                   | I/O      | ST          | Extended IO2 (EIO2)/IRQ0.                                                                                                                                  |  |

| NC         17         —         Reserved: do not connect.           NC         18         —         —         Reserved: do not connect.           EIO3         19         I/O         ST         Extended IO3 (EIO3)/IRQ1/SYNC.           EIO4/SI0         20         I/O         ST         Extended IO4 (EIO4)/Serial Interface 0 (SI0): I²C™_SDA0/SPI_MISO. When I²C™ is used, this line requires an external 1. kΩ pull-up.           EIO5/SI1         21         I/O         ST         Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           EIO6/SI2         22         I/O         ST         Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           EIO7/SI3         23         I/O         ST         Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.           MCLR         24         I/P         ST         Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.           TXD         25         O         Analog         Transmit electrode connection.           NC         26         —         —         Reserved: do not connect.           VSS1         27         P         —   | IS2       | 15                                   | I        | ST          | Interface Selection Pin 2 (IS2).                                                                                                                           |  |

| NC       18       —       —       Reserved: do not connect.         EIO3       19       I/O       ST       Extended IO3 (EIO3)/IRQ1/SYNC.         EIO4/SI0       20       I/O       ST       Extended IO4 (EIO4)/Serial Interface 0 (SI0): I²C™_SDA0/SPI_MISO. When I²C™ is used, this line requires an external 1. kΩ pull-up.         EIO5/SI1       21       I/O       ST       Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         EIO6/SI2       22       I/O       ST       Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         EIO7/SI3       23       I/O       ST       Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         MCLR       24       I/P       ST       Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.         TXD       25       O       Analog       Transmit electrode connection.         NC       26       —       —       Reserved: do not connect.         VSS1       27       P       —       Common ground reference for analog and digital domains.         VDD       28       P       —       Positive supply for peripheral logic and I/                  | NC        | 16                                   | _        | _           | Reserved: do not connect.                                                                                                                                  |  |

| EIO3       19       I/O       ST       Extended IO3 (EIO3)/IRQ1/SYNC.         EIO4/SI0       20       I/O       ST       Extended IO4 (EIO4)/Serial Interface 0 (SI0): I²C™_SDA0/SPI_MISO. When I²C™ is used, this line requires an external 1. kΩ pull-up.         EIO5/SI1       21       I/O       ST       Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         EIO6/SI2       22       I/O       ST       Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         EIO7/SI3       23       I/O       ST       Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         MCLR       24       I/P       ST       Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.         TXD       25       O       Analog       Transmit electrode connection.         NC       26       —       —       Reserved: do not connect.         VDD       28       P       —       Common ground reference for analog and digital domains.         VDD       28       P       —       Common ground reference for analog capacitor (100 nF).                                                                            | NC        | 17                                   | _        | _           | Reserved: do not connect.                                                                                                                                  |  |

| EIO4/SI0  20  I/O  ST  Extended IO4 (EIO4)/Serial Interface 0 (SI0): I²C™_SDA0/SPI_MISO. When I²C™ is used, this line requires an external 1. kΩ pull-up.  EIO5/SI1  21  I/O  ST  Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  EIO6/SI2  22  I/O  ST  Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  EIO7/SI3  23  I/O  ST  Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  MCLR  24  I/P  ST  Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.  TXD  25  O  Analog  Transmit electrode connection.  NC  26  —  Reserved: do not connect.  VSS1  27  P  —  Common ground reference for analog and digital domains.  VDD  28  P  —  Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                      | NC        | 18                                   | _        | _           | Reserved: do not connect.                                                                                                                                  |  |

| SPI_MISO. When I²C™ is used, this line requires an external 1. kΩ pull-up.  EIO5/SI1 21 I/O ST Extended IO5 (EIO5)/Serial Interface 1 (SI1): I²C™_SCL0/SPI_MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  EIO6/SI2 22 I/O ST Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kpull-up.  EIO7/SI3 23 I/O ST Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  MCLR 24 I/P ST Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.  TXD 25 O Analog Transmit electrode connection.  NC 26 — Reserved: do not connect.  VSS1 27 P — Common ground reference for analog and digital domains.  VDD 28 P — Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EIO3      | 19                                   | I/O      | ST          | Extended IO3 (EIO3)/IRQ1/SYNC.                                                                                                                             |  |

| MOSI. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         EIO6/SI2       22       I/O       ST       Extended IO6 (EIO6)/Serial Interface 2 (SI2): I²C™_SDA1/SPI_CS. When I²C™ is used, this line requires an external 1.8 kpull-up.         EIO7/SI3       23       I/O       ST       Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         MCLR       24       I/P       ST       Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.         TXD       25       O       Analog       Transmit electrode connection.         NC       26       —       —       Reserved: do not connect.         VSS1       27       P       —       Common ground reference for analog and digital domains.         VDD       28       P       —       Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                       | EIO4/SI0  | 20                                   | I/O      | ST          | SPI_MISO. When I <sup>2</sup> C™ is used, this line requires an external 1.8                                                                               |  |

| SPI_CS. When I²C™ is used, this line requires an external 1.8 k pull-up.  EIO7/SI3  23  I/O  ST  Extended IO7 (EIO7)/Serial Interface 3 (SI3): I²C™_SCL1/SPI_CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.  MCLR  24  I/P  ST  Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.  TXD  25  O  Analog  Transmit electrode connection.  NC  26  —  Reserved: do not connect.  VSS1  27  P  —  Common ground reference for analog and digital domains.  VDD  28  P  —  Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EIO5/SI1  | 21                                   | I/O      | ST          | Extended IO5 (EIO5)/Serial Interface 1 (SI1): $I^2C^{TM}_SCL0/SPI_MOSI$ . When $I^2C^{TM}$ is used, this line requires an external 1.8 k $\Omega$ pull-up. |  |

| CLK. When I²C™ is used, this line requires an external 1.8 kΩ pull-up.         MCLR       24       I/P       ST       Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 kΩ pull-up.         TXD       25       O       Analog       Transmit electrode connection.         NC       26       —       —       Reserved: do not connect.         VSS1       27       P       —       Common ground reference for analog and digital domains.         VDD       28       P       —       Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EIO6/SI2  | 22                                   | I/O      | ST          | SPI_CS. When I <sup>2</sup> C™ is used, this line requires an external 1.8 kΩ                                                                              |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EIO7/SI3  | 23                                   | I/O      | ST          |                                                                                                                                                            |  |

| NC 26 — Reserved: do not connect.  VSS1 27 P — Common ground reference for analog and digital domains.  VDD 28 P — Positive supply for peripheral logic and I/O pins.  It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MCLR      | 24                                   | I/P      | ST          | Master Clear (Reset) input. This pin is an active-low Reset to the device. It requires external 10 k $\Omega$ pull-up.                                     |  |

| VSS1 27 P — Common ground reference for analog and digital domains.  VDD 28 P — Positive supply for peripheral logic and I/O pins.  It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TXD       | 25                                   | 0        | Analog      | Transmit electrode connection.                                                                                                                             |  |

| VDD 28 P — Positive supply for peripheral logic and I/O pins. It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NC        | 26                                   | _        | _           | Reserved: do not connect.                                                                                                                                  |  |

| It requires an external filtering capacitor (100 nF).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vss1      | 27                                   | Р        |             | Common ground reference for analog and digital domains.                                                                                                    |  |

| EXP 29 P — Exposed pad. It should be connected to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDD       | 28                                   | Р        | _           |                                                                                                                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EXP       | 29                                   | Р        | _           | Exposed pad. It should be connected to Ground.                                                                                                             |  |

**Legend:** P = Power; ST = Schmitt Trigger input with CMOS levels; O = Output; I = Input; — = N/A

### MGC3130

#### **Table of Contents**

| 1.0    | Theory of Operation: Electrical Near-Field (E-Field Sensing) | 5  |

|--------|--------------------------------------------------------------|----|

| 2.0    | Feature Description                                          | 7  |

| 3.0    | System Architecture                                          | 10 |

| 4.0    | Functional Description                                       | 13 |

| 5.0    | Application Architecture                                     | 23 |

| 6.0    | Application Architecture                                     | 24 |

| 7.0    | Hardware Integration                                         | 33 |

| 8.0    | Development Support                                          |    |

| 9.0    | Electrical Specifications                                    | 37 |

| 10.0   | Packaging Information                                        | 38 |

| The Mi | crockin Web Site                                             | 43 |

| Custon | ner Change Notification Service                              | 43 |

| Custon | ner Support                                                  | 43 |

|        | t Identification System                                      |    |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 1.0 THEORY OF OPERATION: ELECTRICAL NEAR-FIELD (E-FIELD) SENSING

Microchip's GestIC is a 3D sensor technology which utilizes an electric field (E-field) for advanced proximity sensing. It allows realization of new user interface applications by detection, tracking and classification of a user's hand or finger motion in free space.

E-fields are generated by electrical charges and propagate three-dimensionally around the surface, carrying the electrical charge.

Applying direct voltages (DC) to an electrode results in a constant electric field. Applying alternating voltages (AC) makes the charges vary over time and thus, the field. When the charge varies sinusoidal with frequency f, the resulting electromagnetic wave is characterized by wavelength  $\lambda$  = c/f, where c is the wave propagation velocity — in vacuum, the speed of light. In cases where the wavelength is much larger than the electrode geometry, the magnetic component is practically zero and no wave propagation takes place. The result is quasi-static electrical near field that can be used for sensing conductive objects such as the human body.

Microchip's GestIC technology uses transmit (Tx) frequencies in the range of 100 kHz which reflects a wavelength of about three kilometers. With electrode geometries of typically less than fourteen by fourteen centimeters, this wavelength is much larger in comparison.

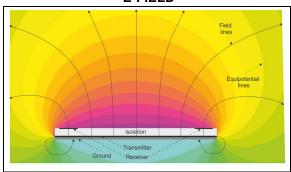

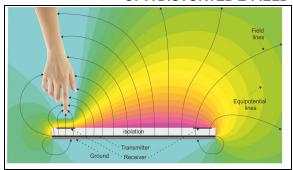

In case a person's hand or finger intrudes the electrical field, the field becomes distorted. The field lines are drawn to the hand due to the conductivity of the human body itself and shunted to ground. The three-dimensional electric field decreases locally. Microchip's GestIC technology uses a minimum number of four receiver (Rx) electrodes to detect the E-field variations at different positions to measure the origin of the electric field distortion from the varying signals received. The information is used to calculate the position, track movements and to classify movement patterns (gestures).

The simulation results in Figure 1-1 and Figure 1-2 show the influence of an earth-grounded body to the electric field. The proximity of the body causes a compression of the equipotential lines and shifts the Rx electrode signal levels to a lower potential which can be measured.

FIGURE 1-1: EQUIPOTENTIAL LINES

OF AN UNDISTORTED

E-FIELD

FIGURE 1-2: EQUIPOTENTIAL LINES

OF A DISTORTED E-FIELD

#### 1.1 GestIC Technology Benefits

- GestIC E-field sensors are not impacted by ambient influences such as light or sound, which have a negative impact to the majority of other 3D technologies.

- The GestIC technology has a high immunity to noise, provides high update rates and resolution, low latency and is also not affected by clothing, surface texture or reflectivity.

- A carrier frequency in the range of 44-115 kHz is being used with the benefit of being outside the regulated radio frequency range. In the same manner, GestIC is not affected by radio interference.

- Usage of thin low-cost materials as electrodes allow low system cost at slim industrial housing designs.

- The further use of existing capacitive sensor structures such as a touch panel's ITO coating allow additional cost savings and ease the integration of the technology.

- Electrodes are invisible to the users' eye since they are implemented underneath the housing surface or integrated into a touch panel's ITO structure.

- GestIC works centrically over the full sensing space. Thus, it provides full surface coverage without any detection blind spots.

- Only one GestIC transmitter electrode is used for E-field generations. The benefit is an overall low power consumption and low radiated EMC noise.

- Since GestIC is basically processing raw electrode signals and computes them in real time into pre-processed gestures and accurate x, y, z positional data, it provides a highly flexible user interface technology for any kind of electronic devices.

#### 2.0 FEATURE DESCRIPTION

#### 2.1 Gesture Definition

A hand gesture is the movement of the hand to express an idea or meaning. The GestIC technology accurately allows sensing of a user's free space hand motion for contact free position tracking, as well as three-dimensional (3D) gesture recognition based on classified movement patterns.

#### 2.2 GestIC Library

MGC3130 is being provided with a GestIC Library, stored on the chip's Flash memory. The library includes:

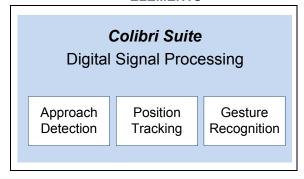

- Colibri Suite: Digital Signal Processing (DSP) algorithms and feature implementations.

- System Control: MGC3130 hardware control features such as Analog Front End (AFE) access, interface control and parameters storage.

- Library Loader: GestIC Library update through the application host's interface.

#### 2.2.1 COLIBRI SUITE

The Colibri Suite combines data acquisition, digital signal processing and interpretation.

The Colibri Suite functional features are illustrated in Figure 2-1 and described in the following sections.

FIGURE 2-1: COLIBRI SUITE CORE ELEMENTS

#### 2.2.1.1 Position Tracking

The Colibri Suite's Position Tracking feature provides three-dimensional hand position over time and area. The absolute position data is provided according to the defined origin of the Cartesian coordinate system (x, y, z). Position Tracking data is continuously acquired in parallel to Gesture Recognition. With a position rate of up to 200 positions/sec., a maximum spatial resolution of 150 dpi is achieved.

#### 2.2.1.2 Gesture Recognition

The Colibri Suite's gesture recognition model detects and classifies hand movement patterns performed inside the sensing area.

Using advanced stochastic classification based on Hidden Markov Model (HMM), industry best gesture recognition rate is being achieved. In addition, there are some gestures derived from the combination of Gesture Recognition and spatial information.

The Colibri Suite includes a set of predefined hand gestures which contains flick, circular and symbol gestures as the ones outlined below:

#### · Flick gestures

A flick gesture is a unidirectional gesture in a quick flicking motion. An example may be a hand movement from West to East within the sensing area, from South to North, etc.

#### · Circular gestures

A circular gesture is a round-shaped hand movement defined by direction (clockwise/counterclockwise) without any specific start position of the user's hand. Two types of circular gestures are distinguished by GestIC technology:

#### 1. Discrete Circles

Discrete Circles are recognized after performing a hand movement inside the sensing area. The recognition result (direction: clockwise/counterclockwise) is provided after the hand movement stops or the hand exits the detection area. The Discrete Circles are typically used as dedicated application control commands.

#### 2. AirWheel

An AirWheel is the recognition of continuously-performed circles inside the sensing area and provides information about the rotational movement in real time. It starts after at least one quadrant of a circle is recognized and provides continuously counter information which increments/decrements according to the movement's direction (clockwise/counterclockwise). The AirWheel can be adjusted for convenient usage in various applications (e.g., volume control, sensitivity adjustment or light dimming).

#### · Sensor Touch Gestures

A Sensor Touch is a multi-zone gesture that reports up to five concurrently-performed touches on the system's electrodes.

The Sensor Touch provides information about Touch and Tapping:

#### 1. Touch

The Sensor Touch indicates an event during which a GestIC electrode is touched. This allows distinction between short and long touches.

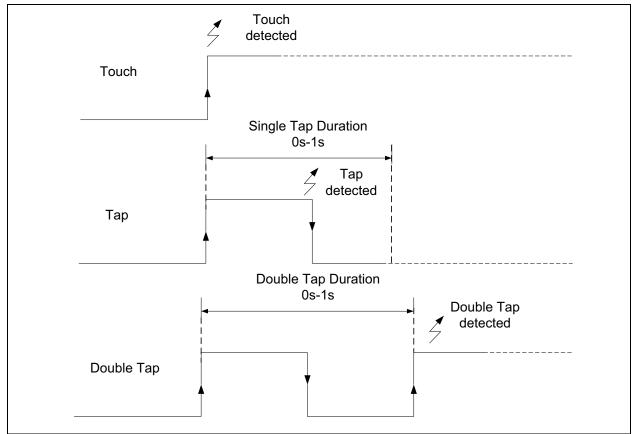

#### 2. Tap and Double Tap

### MGC3130

The Tap and Double Tap signalize short taps and double taps on each system electrode. The Tap length and Double Tap interval are adjustable.

- Single Tap Delay: A Single Tap is detected when touching the surface of an electrode first and after the hand is pulled out of the touch area. The Single Tap is only detected when the timing between the touch and the release of the touch event is smaller than the adjusted delay. Increasing the time allows the user more time to perform the tap. The range for the adjusted delay can be between 0s and 1s.

- Double Tap Delay: The double tap is detected

when two taps are performed within the adjusted delay. The range for the adjusted delay can be between 0s and 1s. The smaller the selected delay is, the faster the two taps have to be executed.

#### FIGURE 2-2: SENSOR TOUCH DIAGRAM

#### Gesture Port

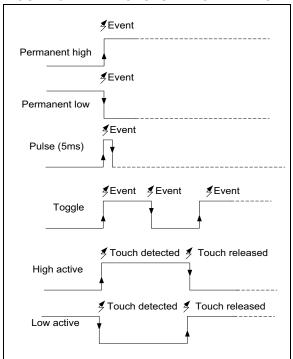

The Gesture Port enables a flexible mapping of Colibri Suite feature events to certain output signals at defined MGC3130's pins. The individual feature events can be mapped to one of five EIO Pins and trigger a variety of signal changes (Permanent high, Permanent low, Toggle, Pulse (5 ms), High Active, Low Active). The Gesture Port simplifies and enhances embedded system integration.

#### 2.2.1.3 Approach Detection

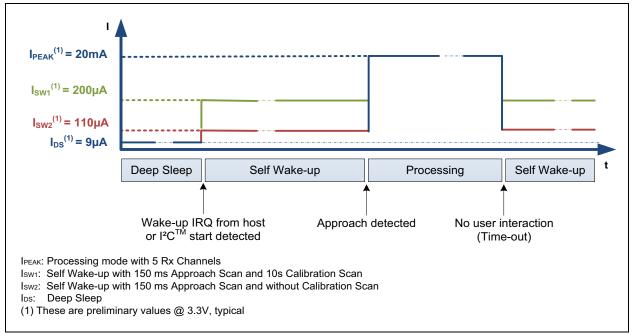

Approach Detection is an embedded power-saving feature of Microchip's Colibri Suite. It sends MGC3130 to Sleep mode and scans periodically the sensing area to detect the presence of a human hand.

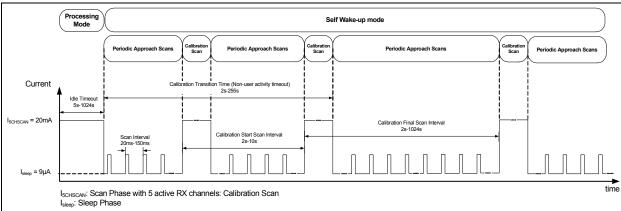

Utilizing the in-built Self Wake-up mode, Approach Detection alternates between Sleep and Scan phases. During the Scan phases, the approach of a human hand can be detected while very low power is consumed. For more details, please see Section 4.2.4.3 "Self Wake-up Mode".

A detected approach of a user exceeding configured threshold criteria will alternate the MGC3130 from Self Wake-up to Processing mode or even the application host in the overall system.

Within the Approach Detection sequence, the following scans are performed:

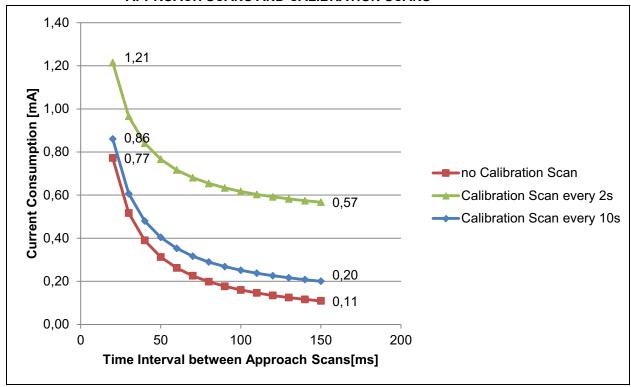

• Approach Scan: An Approach Scan is performed during the Scan phase of the MGC3130's Self Wake-up mode. Typically, 1 Rx channel is active but more channels can be activated via GestIC Library. The time interval (Scan Interval) between two consecutive Approach Scans is configurable. For typical applications, the scan cycle is in a range of 20 ms to 150 ms. During the Approach Scan, the activated Rx channels are monitored for signal changes which are caused by, for example, an approaching human hand and exceeding the defined threshold. This allows an autonomous wake-up of the MGC3130 and host applications at very low-power consumption.

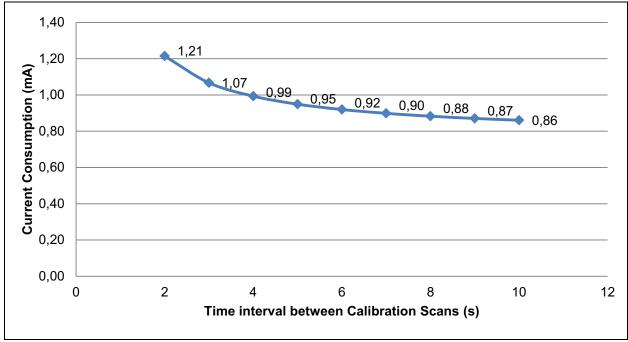

• <u>Calibration Scan</u><sup>(1)</sup>: The Approach Detection feature includes the possibility to perform additional Calibration Scans for the continuous adaptation of the electrode system to environmental changes.

A Calibration Scan is performed during the Scan phase of the MGC3130's Self Wake-up mode. Five Rx channels are active to calibrate the sensor signals. The Calibration Scan is usually performed in configurable intervals from 2s to 1024s.

To reduce the power consumption, the number of scans per second can be decreased after a certain time of non-user activity. Colibri Suite provides a full user flexibility to configure the starting Calibration Scans rate (Calibration Start Scan Interval), non-user activity time-out (Calibration Transition Time) and the Calibration Scans rate (Calibration Final Scan Interval) which will be used afterwards. A typical implementation uses Calibration Scans every 2s during the first two minutes, and every 10s afterwards, until an approach is detected.

**Note 1:** The Calibration Scan is only needed for applications using the Position Tracking feature.

The timing sequence of the Approach Detection feature is illustrated in Figure 2-3.

#### FIGURE 2-3: APPROACH DETECTION SEQUENCE

#### 3.0 SYSTEM ARCHITECTURE

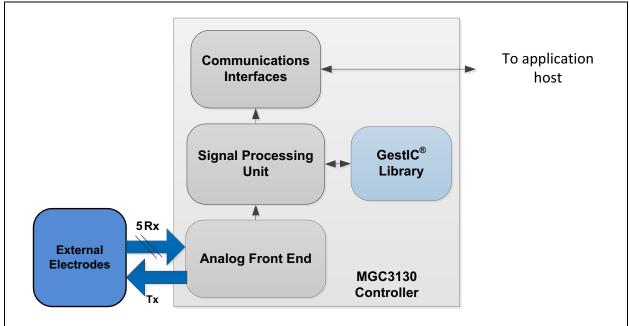

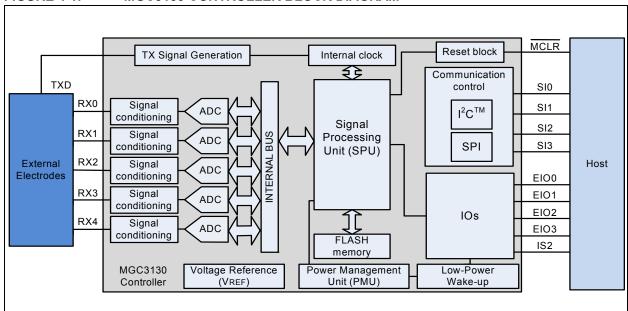

The MGC3130 is the first product based on Microchip's GestIC technology. It is developed as a mixed-signal configurable controller. The entire system solution is composed by three main building blocks (see Figure 3-1):

- MGC3130 Controller

- · GestIC Library

- · External Electrodes

#### 3.1 MGC3130 Controller

The MGC3130 features the following main building blocks:

- Low Noise Analog Front End (AFE)

- Digital Signal Processing Unit (SPU)

- · Flexible Communication Interfaces

It provides a transmit signal to generate the E-field, conditions the analog signals from the receiving electrodes and processes these data digitally on the SPU. Data exchange between the MGC3130 and the host is conducted via the controller's communication interface. For details, please refer to **Section 4.0 "Functional Description"**.

#### 3.2 GestIC Library

The embedded GestIC Library is optimized to ensure continuous and real-time free-space Position Tracking and Gesture Recognition concurrently. It is fully-configurable and allows required parameterization for individual application and external electrodes.

#### 3.3 External Electrodes

Electrodes are connected to MGC3130. An electrode needs to be individually designed for optimal E-field distribution and detection of E-field variations inflicted by a user.

FIGURE 3-1: MGC3130 CONTROLLER SYSTEM ARCHITECTURE

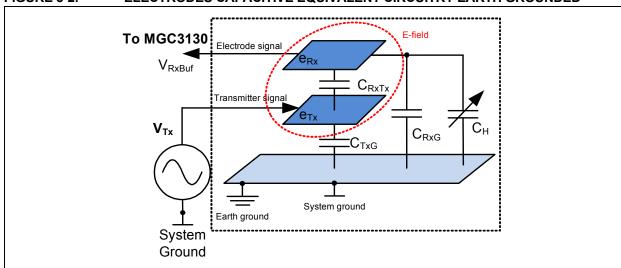

### 3.3.1 ELECTRODE EQUIVALENT CIRCUIT

The hand Position Tracking and Gesture Recognition capabilities of a GestIC system depends on the electrodes design and their material characteristics.

A simplified equivalent circuit model of a generic GestIC electrode system is illustrated in Figure 3-2.

FIGURE 3-2: ELECTRODES CAPACITIVE EQUIVALENT CIRCUITRY EARTH GROUNDED

- V<sub>Tx</sub>: Tx electrode voltage

- V<sub>RxBuf</sub>: MGC3130 Rx input voltage

- C<sub>H</sub>: Capacitance between receive electrode and hand (earth ground). The user's hand can always be considered as earth-grounded due to the comparable large size of the human body.

- C<sub>RXTx</sub>: Capacitance between receive and transmit electrodes

- C<sub>RXG</sub>: Capacitance of the receive (Rx) electrode to system ground + input capacitance of the MGC3130 receiver circuit

- C<sub>TxG</sub>: Capacitance of the transmit (Tx) electrode to system ground

- e<sub>Rx</sub>: Rx electrode

- e<sub>Tx</sub>: Tx electrode

The Rx and Tx electrodes in a GestIC electrode system build a capacitance voltage divider with the capacitances  $C_{RxTx}$  and  $C_{RxG}$  which are determined by the electrode design.  $C_{TxG}$  represents the Tx electrode capacitance to system ground driven by the Tx signal. The Rx electrode measures the potential of the generated E-field. If a conductive object (e.g., a hand) approaches the Rx electrode,  $C_{H}$  changes its capacitance. This minuscule change in the femtofarad range is detected by the MGC3130 receiver.

The equivalent circuit formula for the earth-grounded circuitry is described in Equation 3-1.

EQUATION 3-1: ELECTRODES EQUIVALENT CIRCUIT

$$V_{RxBuf} = V_{Tx} \times \frac{C_{RxTx}}{C_{RxTx} + C_{RxG} + C_{H}}$$

A common example of an earth-grounded device is a notebook, even with no ground connection via power supply or ethernet connection. Due to its larger form factor, it presents a high earth-ground capacitance in the range of 50 pF and thus, it can be assumed as an earth-grounded GestIC system.

A brief overview of the typical values of the electrodes capacitances is summarized in Table 3-1.

TABLE 3-1: ELECTRODES

CAPACITANCES TYPICAL

VALUES

| Capacity          | Typical Value |

|-------------------|---------------|

| C <sub>RxTx</sub> | 1030 pF       |

| C <sub>TxG</sub>  | 101000 pF     |

| C <sub>RxG</sub>  | 1030 pF       |

| C <sub>H</sub>    | <1 pF         |

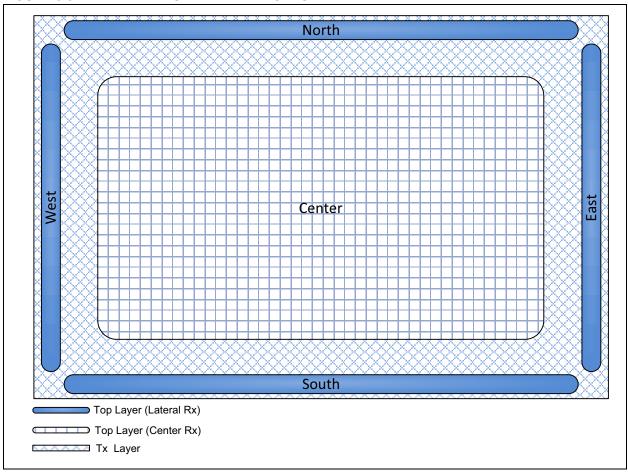

#### 3.3.2 STANDARD ELECTRODE DESIGN

The MGC3130 electrode system is typically a double-layer design with a Tx transmit electrode at the bottom layer to shield against device ground and thus, ensure high receive sensitivity. Up to five comparably smaller Rx electrodes are placed above the Tx layer providing the spatial resolution of the GestIC system. Tx and Rx

are separated by a thin isolating layer. The Rx electrodes are typically arranged in a frame configuration as shown in Figure 3-3. The frame defines the inside sensing area with maximum dimensions of 14x14 centimeters. An optional fifth electrode in the center of the frame may be used to improve the distance measurement and add simple touch functionality.

The electrodes' shapes can be designed solid or structured. In addition to the distance and the material between the Rx and Tx electrodes, the shape structure density also controls the capacitance  $C_{RXTX}$  and thus, the sensitivity of the system.

FIGURE 3-3: FRAME SHAPE ELECTRODES

#### 4.0 FUNCTIONAL DESCRIPTION

Microchip Technology's MGC3130 configurable controller uses up to five E-field receiving electrodes. Featuring a Signal Processing Unit (SPU), a wide range of 3D gesture applications are being preprocessed on the MGC3130, which allows short development cycles.

Always-on 3D sensing, even for battery-driven mobile devices, is enabled due to the chip's low-power design and variety of programmable power modes. A Self Wake-up mode triggers interrupts to the application host reacting to interaction of a user with the device and supporting the host system in overall power reduction.

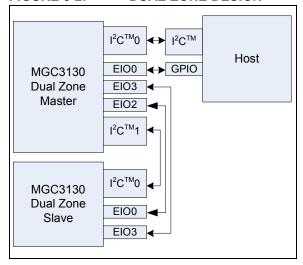

Featuring a programmable 4-pin digital interface, the MGC3130 matches a multitude of hardware requirements. Developers have the choice of data exchange via I<sup>2</sup>C or SPI. Since the device provides two I<sup>2</sup>C interfaces, developers have the option to set up a master-slave architecture between two MGC3130 devices to add an additional sensing area (e.g., Two-

Zone Design) or a single MGC3130 and another circuit with a corresponding interface, such as a touch screen controller.

GestIC sensing electrodes are driven by a low-voltage signal with a frequency in the range of 100 kHz, which allows their electrical conductive structure to be made of any low-cost material. Even the reuse of existing conductive structures, such as a display's ITO coating, is feasible, making the MGC3130 an overall, very cost-effective system solution.

Figure 4-1 provides an overview of the main building blocks of MGC3130. These blocks will be described in the following sections.

FIGURE 4-1: MGC3130 CONTROLLER BLOCK DIAGRAM

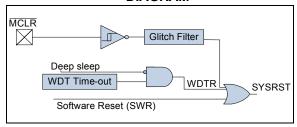

#### 4.1 Reset Block

The Reset block combines all Reset sources. It controls the device system's Reset signal (SYSRST). The following is a list of device Reset sources:

- MCLR: Master Clear Reset pin

- SWR: Software Reset available through GestIC Library

- · WDTR: Watchdog Timer Reset

A simplified block diagram of the Reset block is illustrated in Figure 4-2.

FIGURE 4-2: SYSTEM RESET BLOCK DIAGRAM

#### 4.2 Power Control and Clocks

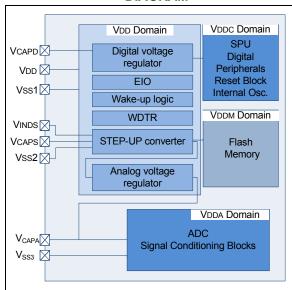

#### 4.2.1 POWER MANAGEMENT UNIT (PMU)

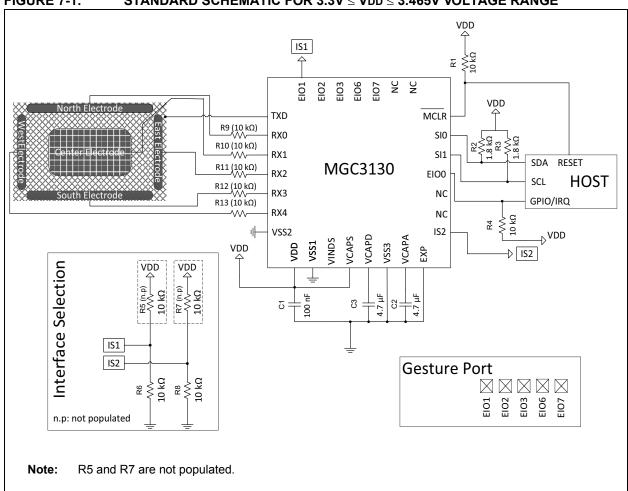

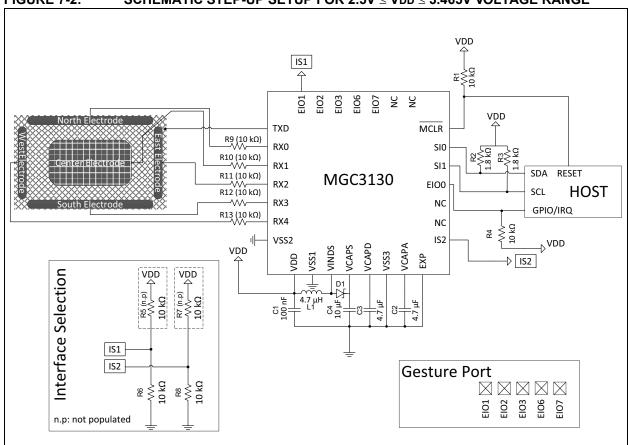

The device requires a  $3.3V \pm 5\%$  supply voltage at VDD. Enabling the internal STEP-UP converter extends the voltage range to 2.5 to 3.465V.

According to Figure 4-3, the used power domains are as follows:

- VDD Domain: This domain is powered by VDD = 2.5V to 3.465V (typical VDD = 3.3V). VDD is the external power supply for EIO, wake-up logic, WDTR, internal regulators and STEP-UP converter. It is provided externally through the VDD pin.

- VDDC Domain: This domain is powered by VDDC = 1.8V. It is generated by an embedded low-impedance and fast linear voltage regulator. The voltage regulator is working under all conditions (also during Deep Sleep mode) preserving the MGC3130 data context. VDDC is the internal power supply voltage for digital blocks, Reset block and RC oscillators. An external block capacitor, CEFCD, is required on VCAPD pin.

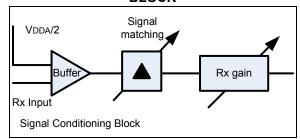

- VDDA Domain: This domain is powered by VDDA = 3.0V. It is generated by an embedded lowimpedance and fast linear voltage regulator. During Deep Sleep mode, the analog voltage regulator is switched off. VDDA is the internal analog power supply voltage for the ADCs and the signal conditioning. An external block capacitor, CEFCA, is required on VCAPA pin.

- VDDM Domain: This domain is powered by VDDM = 3.3V. VDDM is the internal power supply voltage for the internal Flash memory. This power supply is depending on VDD voltage range. If VDD ≥ 3.3V, the memory is directly powered through the VDD pin. In case of VDD < 3.3V, the Flash power supply is generated internally by an embedded STEP-UP converter.</li>

FIGURE 4-3: POWER SCHEME BLOCK DIAGRAM

• STEP-UP Converter: The STEP-UP converter is generating 3.3V from the connected supply voltage VDD (if it is lower than 3.3V). This voltage is required by the internal Flash memory. The required voltage reference is taken from the voltage reference block. During Deep Sleep mode, the converter is switched off. It requires an external connected inductor, a filtering capacitor and a Schottky diode connected to the VINDs and VCAPS pins. If the supply voltage is high enough, the STEP-UP converter will be disabled. Please refer to Section 9.0 "Electrical Specifications" for more details.

#### 4.2.2 POWER SUPERVISORS

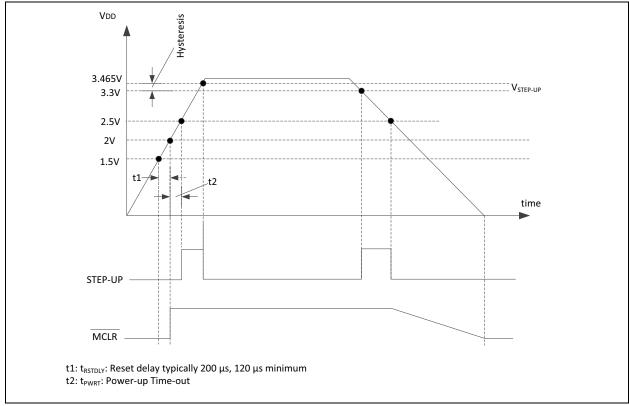

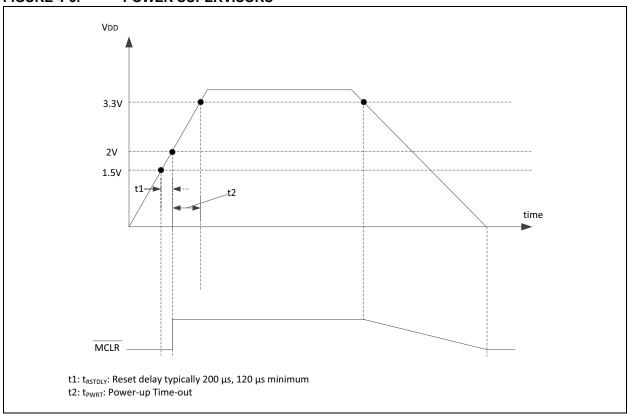

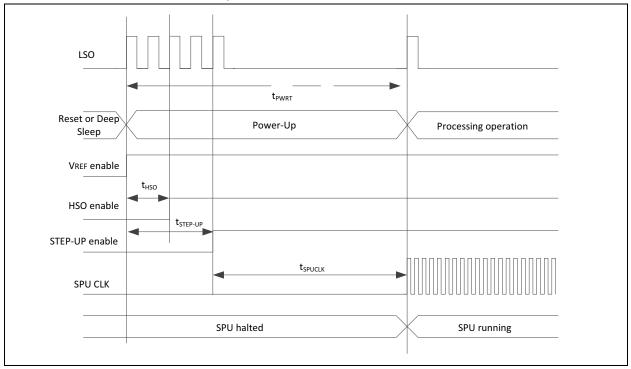

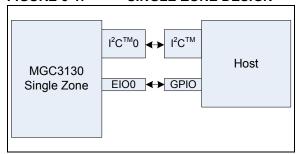

During the Power-up sequence, the system is kept under Reset condition for approximately 200  $\mu$ s (Reset delay:  $t_{RSTDLY}$ ) after the VDD =1.5V voltage is reached (1.2V minimum). During this delay, the system Reset will remain low and the VDD should reach typically 2V.